# PRODUCT OVERVIEW

# INTRODUCTION

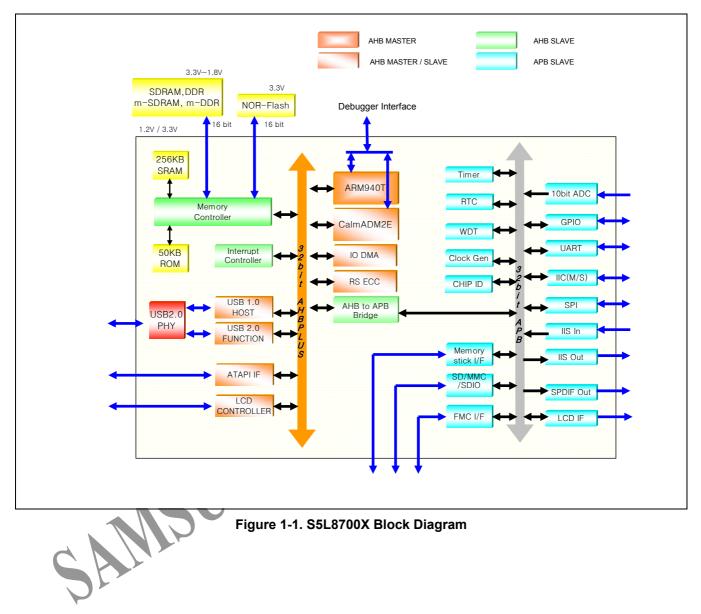

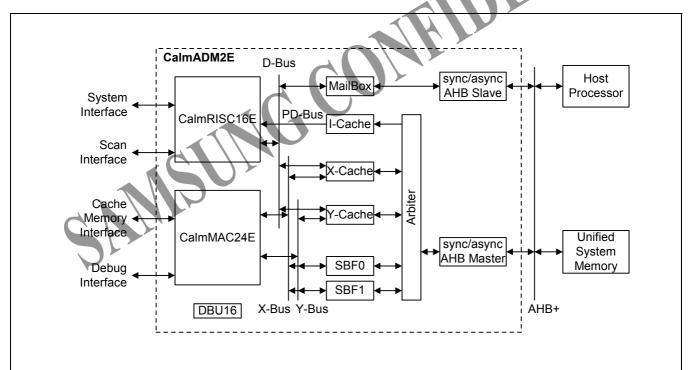

S5L8700X is an audio player IC supporting various compressed audio format on Flash Memory Media and Hard Disk. S5L8700X provides 256Kbytes of SRAM and it supports optional external SDRAM. An ARM940T<sup>TM</sup> is provided as a CPU and an 16bit RISC processor (CalmRISC16<sup>TM</sup>) and 24bit MAC(MAC2424<sup>TM</sup>) are provided as a DSP function.

# FEATURES

- AMBA BUS Architecture(100Mhz)

- ARM940T (200Mhz)

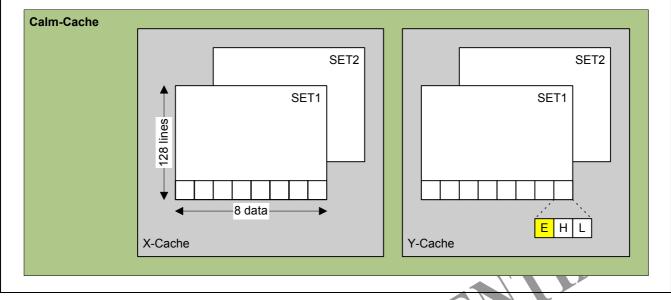

- CalmADM2E(130Mhz) CalmRISC16 + MAC2424 with 4KB of Instruction Cache

- 6KB of X Cache

- 6KB of Y Cache

- IO DMA (4 ch)

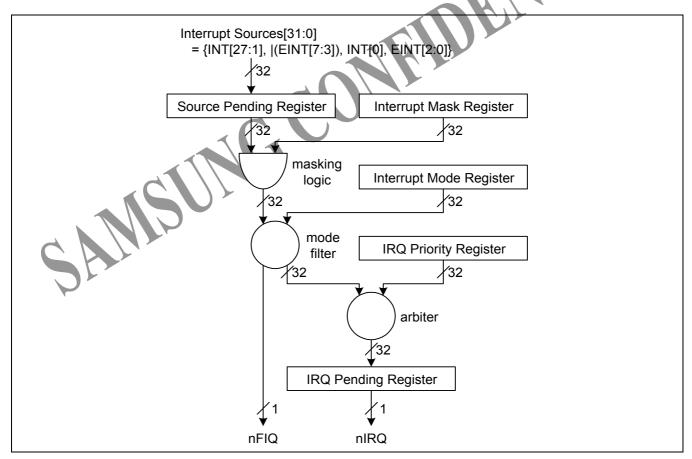

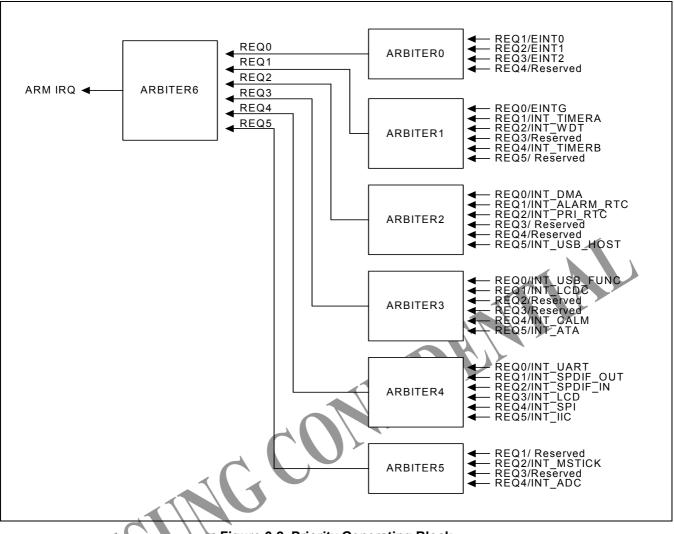

- INTERRUPTS (8ch ext interrupt)

- MEMORIES

256K Byte embedded SRAM

50K Byte embedded ROM

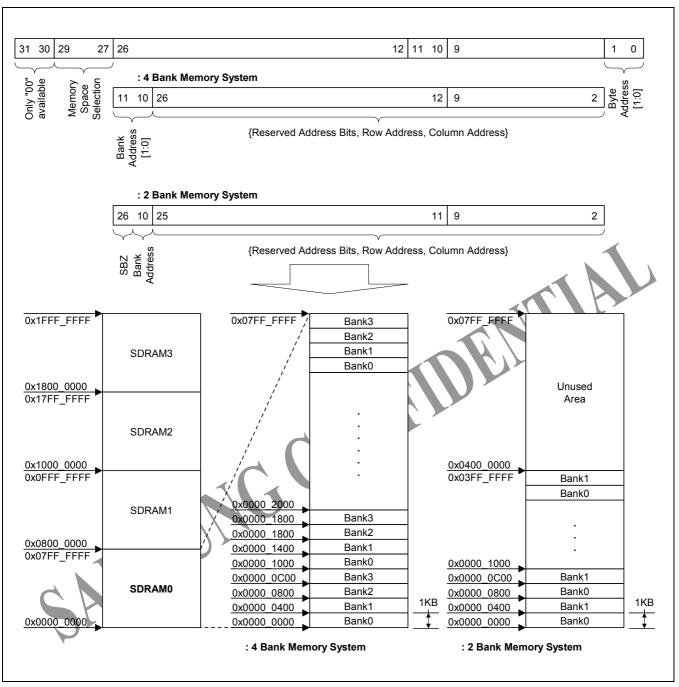

SDRAM(16bit, 3.3V), mSDRAM(16bit, 1.8V)

DDR SDRAM(16bit, 2.7V), mDDR(16bit, 1.8V)

( support 3 chip select)

NOR Flash

( support 3 chip select)

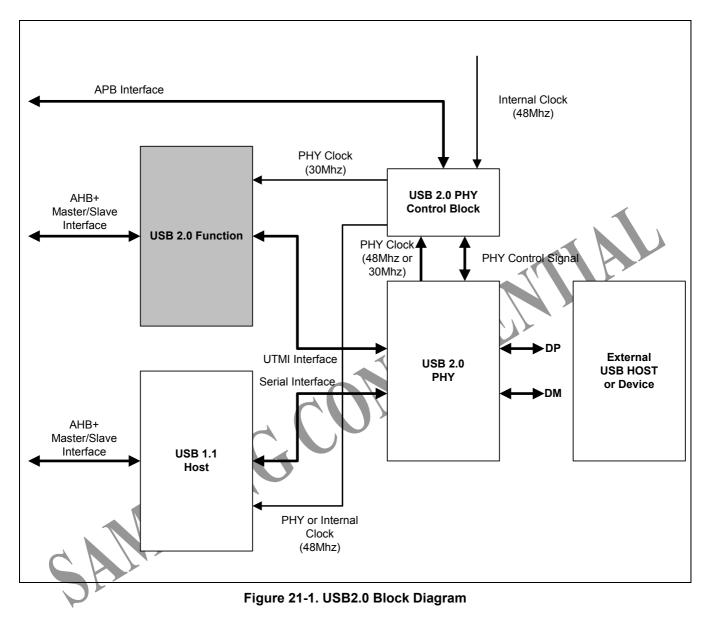

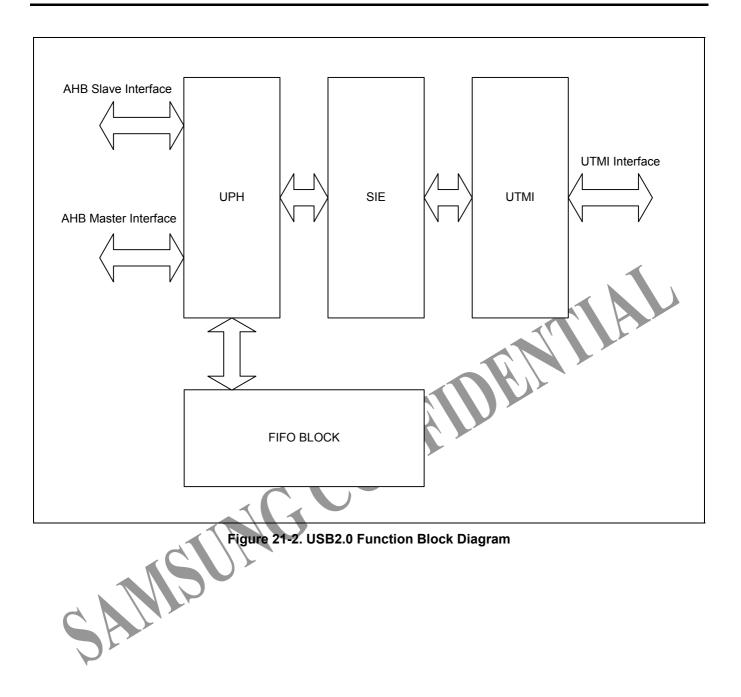

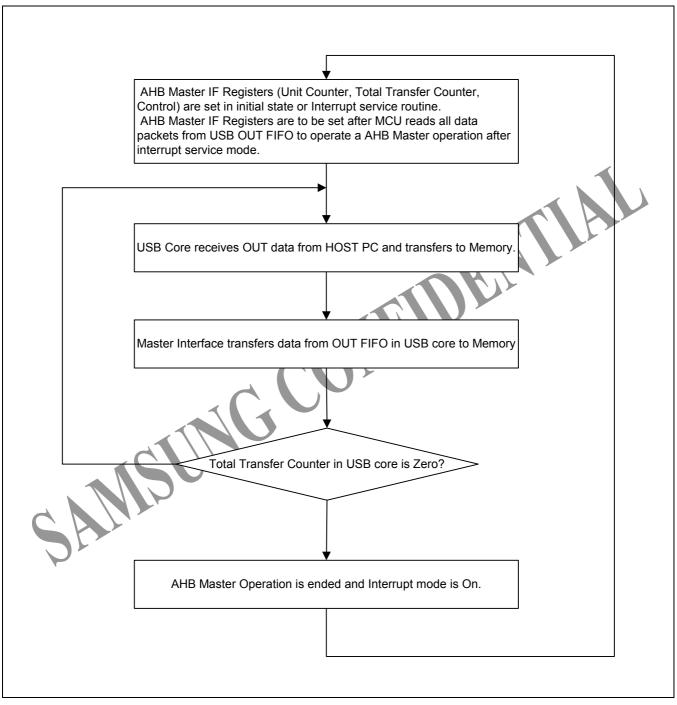

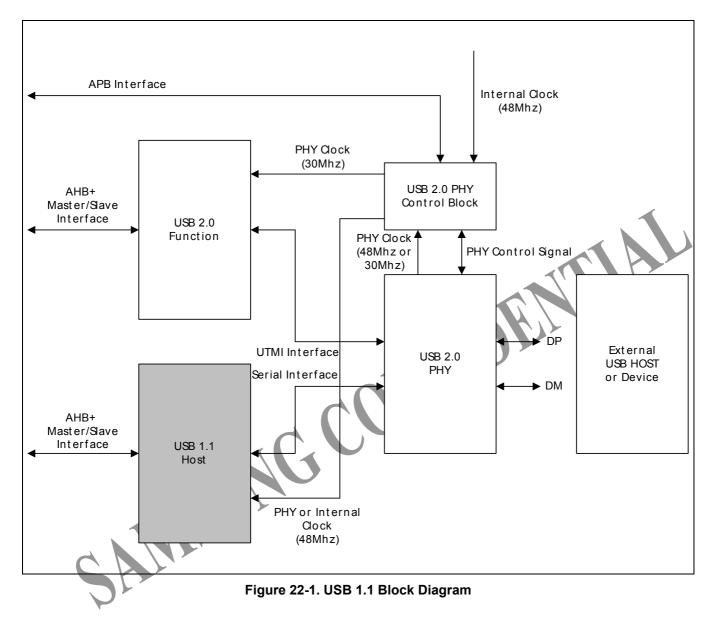

- USB 1.1 Host

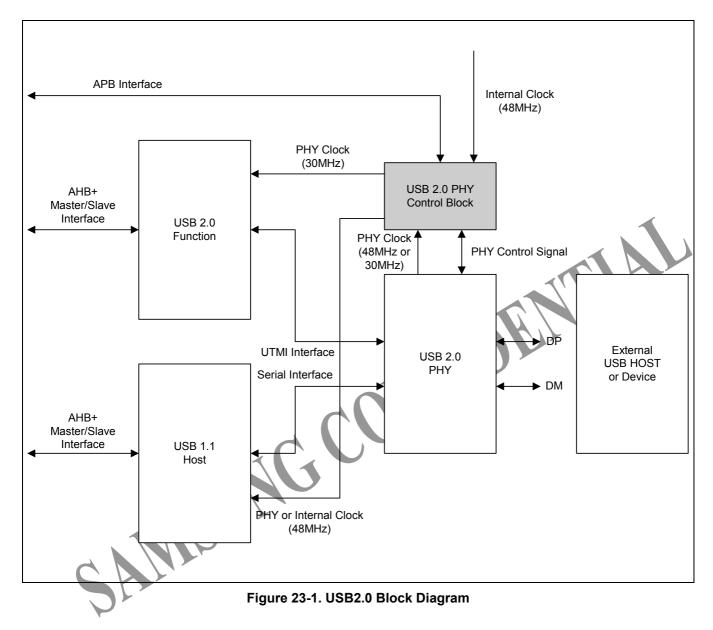

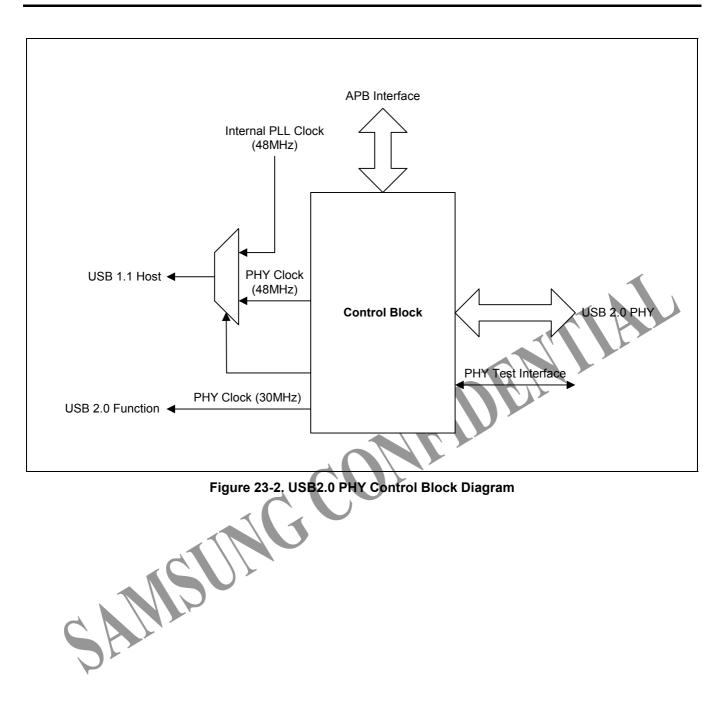

- USB2.0 Function

- ATAPI Host Controller

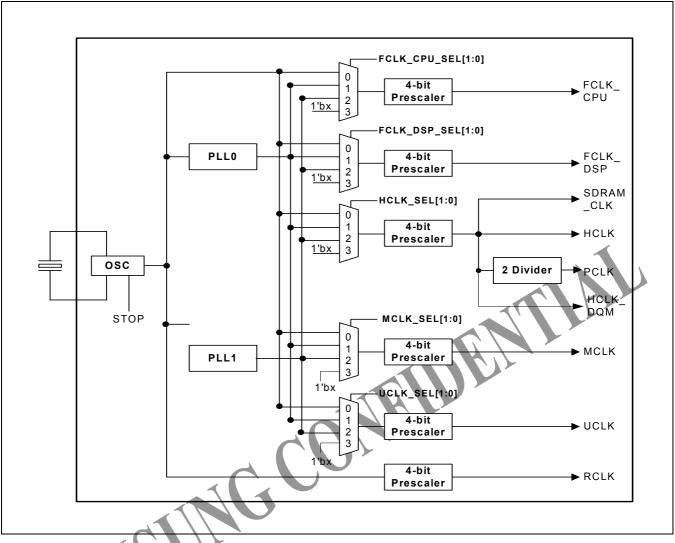

- X-TAL & PLL 32.768kHz X-tal for system clock source. 24MHz(or 48MHz) X-tal for USB2.0 phy Maximum PLL Frequency : 300MHz

- NAND Flash / Smart Media Card (SMC) -MLC type NAND Flash support

- MMC/SD card interface

- Support MMC 4.0 spec, SD 1.0 spec, SDIO

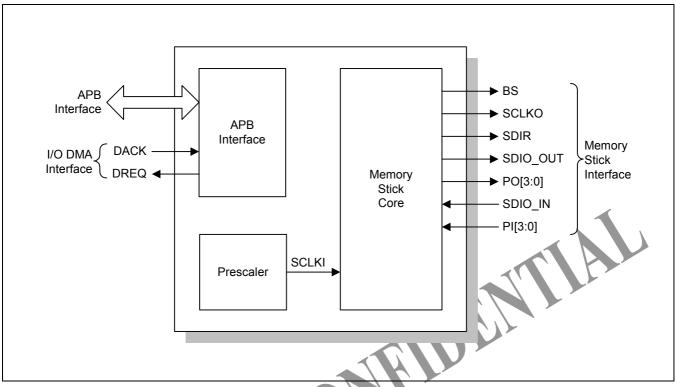

- Memory Stick interface Host controller version 1.3

- LCD INTERFACE

- 4/8/16 bit parallel & serial interface

- Color LCD

- 1/2/4/8bpp Palletized and

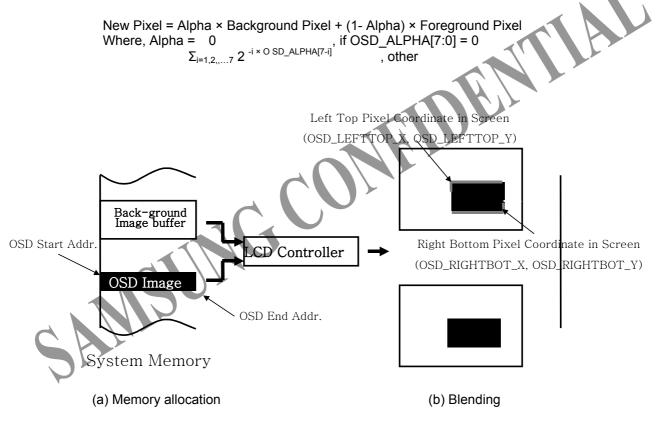

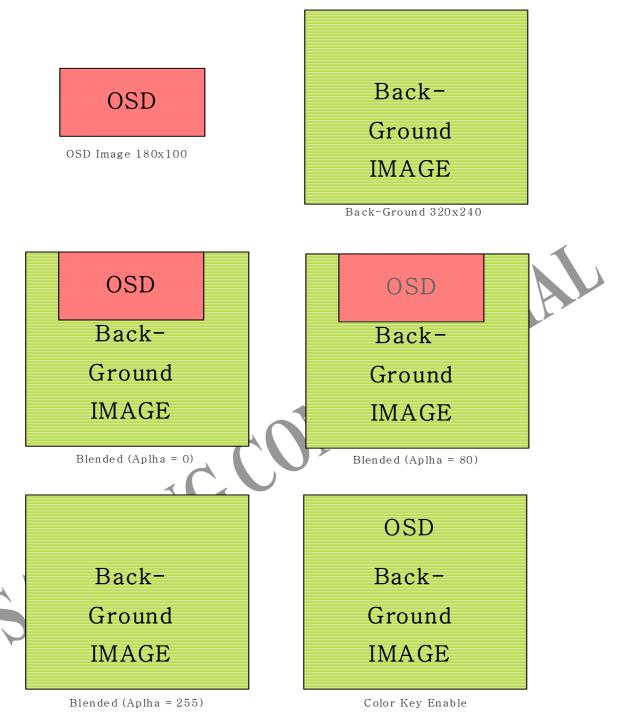

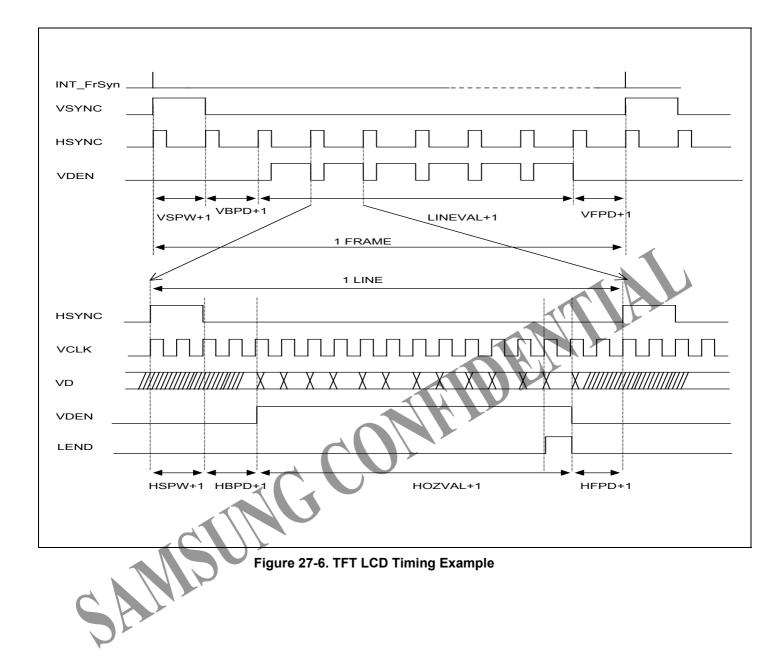

16bpp/24-bpp Non-Palletized Color-TFT support 320x240, 640x480 up to 2048x2048 Maximum 2K x 2K x 4 virtual screen size OSD(On Screen Display) multiplexing Alpha blending

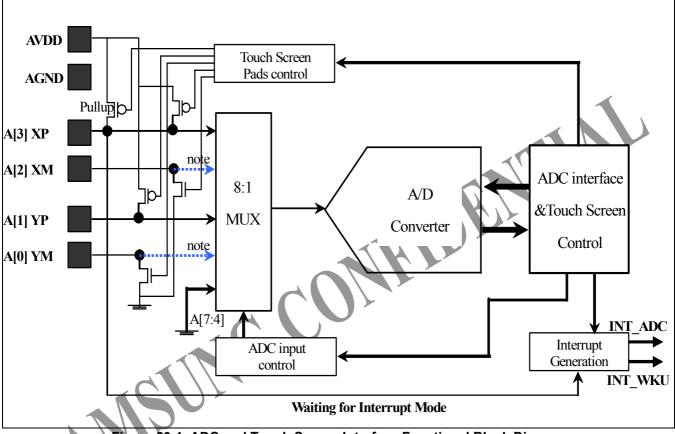

- TSADC :10bit 4 channel adc ( support Touch Screen )

- IIS OUT/ IIS IN

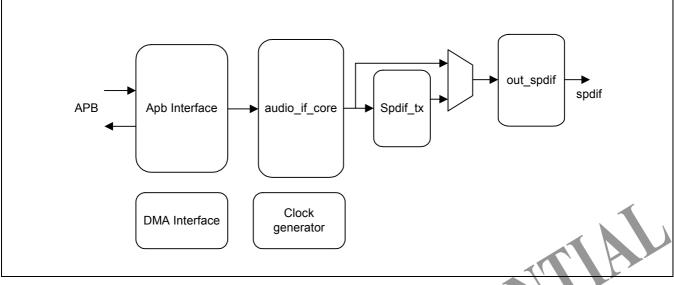

- SPDIF out/ UART / IIC / SPI /

- Chip ID (40bit unique user-id)

- Real Timer Clock (RTC)

- General-Purpose Input/Output (GPIO)

- 16-bit timer(4ch)

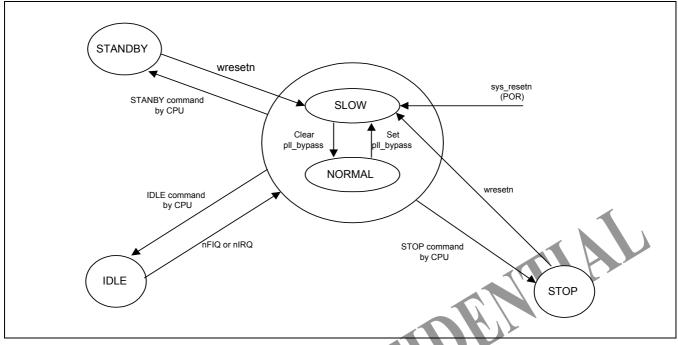

- POWER MANAGEMENT

- Digital data recording/playback system utilizing EEPROM and ROM memories as a storage medium – U.S. Patent No. 5,535,356

- Digital storage system adopting semiconductor memory device – U.S. Patent No. 5,623,623

#### **TYPICAL APPLICATION**

Digital Audio Player

#### **ORDERING INFORMATION**

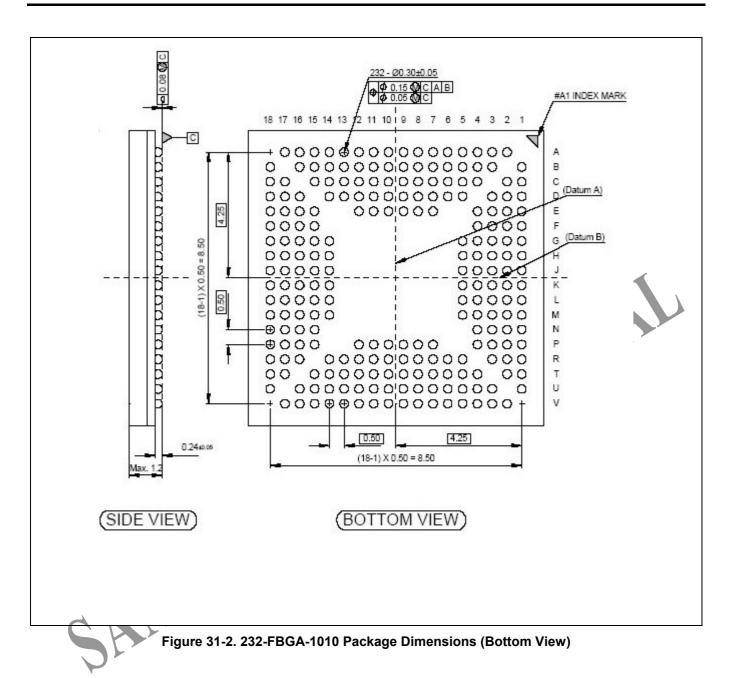

| Device   | Package             | Operating Temperature |

|----------|---------------------|-----------------------|

| S5L8700X | 232-FBGA-1010 (0.5) | –20  °C ~ +70  °C     |

SAMSUNG COMPUTATION

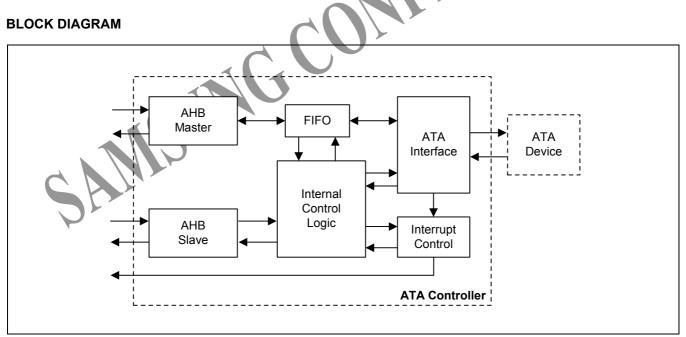

# **BLOCK DIAGRAM**

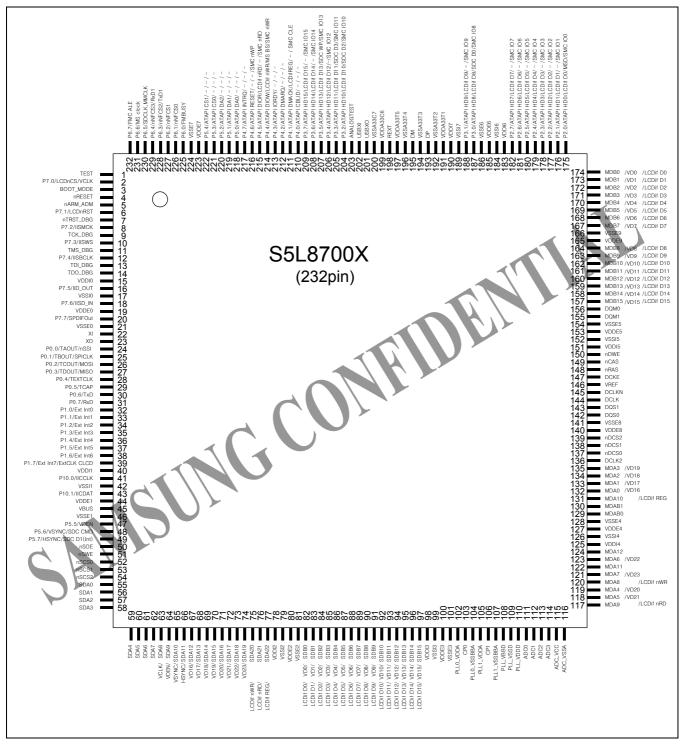

# **PIN ASSIGNMENTS**

Figure 1-2. S5L8700X Pin Assignments (232-FBGA)

# **PIN DESCRIPTION**

| Pin Name          | I/O            | Туре               | Pin Description                                     | Pin        | ETC |

|-------------------|----------------|--------------------|-----------------------------------------------------|------------|-----|

| System            |                | 4                  |                                                     |            | 1   |

| TEST              | 1              | phic               | Test enable                                         | 1          | Τ   |

| BOOT_MODE         |                | phic               | Test clock/ Boot bypass mode(active high)           | 3          |     |

| nRESET            |                | phic               | Global Reset input (active low)                     | 4          |     |

| nARM_ADM          |                | phic               | JTAG select (0:ARM, 1:ADM)                          | 5          |     |

| XI                | I              | phsosck1           | Crystal in                                          | 22         |     |

| XO                | 0              | phsosck1           | Crystal out                                         | 23         |     |

| ARM940T Debugger  |                | •                  |                                                     |            |     |

| nTRST_DBG         | l(up)          | phicu              | Tap controller reset (active low) for JTAG.         | 7          |     |

| TCK_DBG           | l(up)          | phicu              | JTAG Clock Input                                    | 9          |     |

| TMS_DBG           | l(up)          | phicu              | Tap controller Machine State control for JTAG       | 11         |     |

| TDI_DBG           | l(up)          | phicu              | Test data input for JTAG                            | 13         |     |

| TDO_DBG           | 0              | phob4              | Test data output for JTAG                           | 14         |     |

| ADM Debugger & Ex | cternal interr | upt & Touch Screen |                                                     | - <b>,</b> |     |

| nTRST_ADM         | В              | phbct4             | P1.3 / ext int3 / TS_PUON                           | 35         | Τ   |

| TCK_ADM           | В              | phbct4             | P1.4 / ext int4 / TS_XPON                           | 36         |     |

| TMS_ADM           | В              | phbct4             | P1.5 / ext int5 / TS_XMON                           | 37         |     |

| TDI_ADM           | В              | phbct4             | P1.6 / ext int6 / TS_YPON                           | 38         |     |

| TDO_ADM           | В              | phbct4             | P1.7 / ext int7 / TS_YMON / ExtCLK CLCD             | 39         |     |

| System PLL0, PLL  | 1              |                    |                                                     | •          | -   |

| PLL0_VDDA         | P              | vdd12t_abb         | 1.2V analog power for PLL0 circuitry                | 102        | Ι   |

| CP0               | 0              | poar50_pll_abb     | filter for PLL0 circuitry                           | 103        |     |

| PLL0_VSSBBA       | P              | vssbb_abb          | 1.2V analog ground and bulk bias for PLL0 circuitry | 104        |     |

| PLL1_VDDA         | Р              | vdd12t_abb         | 1.2V analog power for PLL1 circuitry                | 105        |     |

| CP1               | 0              | poar50_pll_abb     | filter for PLL1 circuitry                           | 106        | 1   |

| PLL1_VSSBBA       | Р              | vssbb_abb          | 1.2V analog ground and bulk bias for PLL1 circuitry | 107        | 1   |

| PLL_VBBD          | Р              | vbb_abb            | 1.2V digital bulk bias for PLL0, PLL1               | 108        | 1   |

| PLL_VSSD          | Р              | vsst_abb           | 1.2V digital ground for PLL0, PLL1(Double bonding)  | 109        |     |

| PLL_VDDD          | Р              | vdd12t_abb         | 1.2V digital power for PLL0, PLL1(Double bonding)   | 110        |     |

# Table 1-1. S5L8700X Pin Descriptions

| Pin Name         | I/O | Туре     | Pin Description                                 | Pin | ETC |

|------------------|-----|----------|-------------------------------------------------|-----|-----|

| NOR Flash & SDRA | И   |          |                                                 |     |     |

| nSOE             | В   | pvbct8cd | Nor flash output enable                         | 50  |     |

| nSWE             | В   | pvbct8cd | Nor flash write enable                          | 51  |     |

| nSCS0            | В   | pvbct8cd | Nor flash Chip select for static memory space 0 | 52  |     |

| nSCS1            | В   | pvbct8cd | Chip select for static memory space 1           | 53  |     |

| nSCS2            | В   | pvbct8cd | Chip select for static memory space 2           | 54  |     |

| SA0              | В   | pvbct8cd | Address 22 to 0 for NOR Flash                   | 55  |     |

| SA1              | В   | pvbct8cd | Address 22 to 0 for NOR Flash                   | 56  |     |

| SA2              | В   | pvbct8cd | Address 22 to 0 for NOR Flash                   | 57  |     |

| SA3              | В   | pvbct8cd | Address 22 to 0 for NOR Flash                   | 58  |     |

| SA4              | В   | pvbct8cd | Address 22 to 0 for NOR Flash                   | 59  |     |

| SA5              | В   | pvbct8cd | Address 22 to 0 for NOR Flash                   | 60  |     |

| SA6              | В   | pvbct8cd | Address 22 to 0 for NOR Flash                   | 61  |     |

| SA7              | В   | pvbct8cd | Address 22 to 0 for NOR Flash                   | 62  |     |

| SA8              | В   | pvbct8cd | Address 22 to 0 for NOR Flash                   | 63  |     |

| SA9              | В   | pvbct8cd | Address 22 to 0 for NOR Flash                   | 64  |     |

| SA10             | В   | pvbct8cd | Address 22 to 0 for NOR Flash                   | 65  |     |

| SA11             | В   | pvbct8cd | Address 22 to 0 for NOR Flash                   | 66  |     |

| SA12             | В   | pvbct8cd | Address 22 to 0 for NOR Flash                   | 67  |     |

| SA13             | В   | pvbct8cd | Address 22 to 0 for NOR Flash                   | 68  |     |

| SA14             | В   | pvbct8cd | Address 22 to 0 for NOR Flash                   | 69  |     |

| SA15             | В   | pvbct8cd | Address 22 to 0 for NOR Flash                   | 70  |     |

| SA16             | B   | pvbct8cd | Address 22 to 0 for NOR Flash                   | 71  |     |

| SA17             | В   | pvbct8cd | Address 22 to 0 for NOR Flash                   | 72  |     |

| SA18             | В   | pvbct8cd | Address 22 to 0 for NOR Flash                   | 73  |     |

| SA19             | В   | pvbct8cd | Address 22 to 0 for NOR Flash                   | 74  |     |

| SA20             | В   | pvbct8cd | Address 22 to 0 for NOR Flash                   | 75  |     |

| SA21             | В   | pvbct8cd | Address 22 to 0 for NOR Flash                   | 76  |     |

| SA22             | В   | pvbct8cd | Address 22 to 0 for NOR Flash                   | 77  |     |

| SDB0             | В   | pvbct8cd | Data 15 to 0 for NOR flash                      | 82  |     |

| SDB1             | В   | pvbct8cd | Data 15 to 0 for NOR flash                      | 83  |     |

| SDB2             | В   | pvbct8cd | Data 15 to 0 for NOR flash                      | 84  |     |

| SDB3             | В   | pvbct8cd | Data 15 to 0 for NOR flash                      | 85  |     |

| SDB4             | В   | pvbct8cd | Data 15 to 0 for NOR flash                      | 86  |     |

| SDB5             | В   | pvbct8cd | Data 15 to 0 for NOR flash                      | 87  | 1   |

| SDB6             | В   | pvbct8cd | Data 15 to 0 for NOR flash                      | 88  |     |

# Table 1-1. S5L8700X Pin Descriptions (Continued)

| Pin Name | I/O Туре |                  | Pin Description             | Pin | ETC |

|----------|----------|------------------|-----------------------------|-----|-----|

| SDB7     | В        | pvbct8cd         | Data 15 to 0 for NOR flash  | 89  |     |

| SDB8     | В        | pvbct8cd         | Data 15 to 0 for NOR flash  | 90  |     |

| SDB9     | В        | pvbct8cd         | Data 15 to 0 for NOR flash  | 91  |     |

| SDB10    | В        | pvbct8cd         | Data 15 to 0 for NOR flash  | 92  |     |

| SDB11    | В        | pvbct8cd         | Data 15 to 0 for NOR flash  | 93  |     |

| SDB12    | В        | pvbct8cd         | Data 15 to 0 for NOR flash  | 94  |     |

| SDB13    | В        | pvbct8cd         | Data 15 to 0 for NOR flash  | 95  |     |

| SDB14    | В        | pvbct8cd         | Data 15 to 0 for NOR flash  | 96  |     |

| SDB15    | В        | pvbct8cd         | Data 15 to 0 for NOR flash  | 97  |     |

| DCLK2    | В        | psbsstl_8700     | SDRAM clock                 | 136 |     |

| VREF     | I        | phia_8700        | DDR SDRAM VREF              | 146 |     |

| DQS0     | В        | psbsstl_8700     | DDR SDRAM LDQS              | 142 |     |

| DQS1     | В        | psbsstl_8700     | DDR SDRAM UDQS              | 143 |     |

| DCLKN    | 0        | psosstldiff_8700 | DDR SDRAM CLKB              | 145 |     |

| DCLK     | 0        | psosstldiff_8700 | DDR SDRAM CLK               | 144 |     |

| DCKE     | В        | psbsstl_8700     | SDRAM clock enable          | 147 |     |

| DQM0     | В        | psbsstl_8700     | SDRAM Data mask [7:0]       | 156 |     |

| DQM1     | В        | psbsstl_8700     | SDRAM Data mask [15:8]      | 155 |     |

| nDCS0    | В        | psbsstl_8700     | SDRAM Chip select0          | 137 |     |

| nDCS1    | В        | psbsstl_8700     | SDRAM Chip select1          | 138 |     |

| nDCS2    | В        | psbsstl_8700     | SDRAM Chip select2          | 139 |     |

| nDWE     | В        | psbsstl_8700     | SDRAM write enable          | 150 |     |

| nRAS     | B        | psbsstl_8700     | SDRAM raw address strobe    | 148 |     |

| nCAS     | В        | psbsstl_8700     | SDRAM column address strobe | 149 |     |

| MDA0     | В        | psbsstl_8700     | Address 12 to 0 for SDRAM   | 132 |     |

| MDA1     | В        | psbsstl_8700     | Address 12 to 0 for SDRAM   | 133 |     |

| MDA2     | В        | psbsstl_8700     | Address 12 to 0 for SDRAM   | 134 |     |

| MDA3     | В        | psbsstl_8700     | Address 12 to 0 for SDRAM   | 135 |     |

| MDA4     | В        | psbsstl_8700     | Address 12 to 0 for SDRAM   | 119 |     |

| MDA5     | В        | psbsstl_8700     | Address 12 to 0 for SDRAM   | 118 |     |

| MDA6     | В        | psbsstl_8700     | Address 12 to 0 for SDRAM   | 123 |     |

| MDA7     | В        | psbsstl_8700     | Address 12 to 0 for SDRAM   | 121 |     |

| MDA8     | В        | psbsstl_8700     | Address 12 to 0 for SDRAM   | 120 |     |

| MDA9     | В        | psbsstl_8700     | Address 12 to 0 for SDRAM   | 117 |     |

| MDA10    | В        | psbsstl_8700     | Address 12 to 0 for SDRAM   | 131 | ĺ   |

| MDA11    | В        | psbsstl_8700     | Address 12 to 0 for SDRAM   | 122 | ĺ   |

| MDA12    | В        | psbsstl_8700     | Address 12 to 0 for SDRAM   | 124 | 1   |

Table 1-1. S5L8700X Pin Descriptions (Continued)

| Pin Name   | I/O | Туре         | Pin Description                                      | Pin | ETC      |  |

|------------|-----|--------------|------------------------------------------------------|-----|----------|--|

| MDBA0      | В   | psbsstl_8700 | Bank 0 address for SDRAM                             | 129 | 1        |  |

| MDBA1      | В   | psbsstl_8700 | Bank 1 address for SDRAM                             |     |          |  |

| MDB0       | В   | psbsstl_8700 | Data 15 to 0 for SDRAM                               | 174 |          |  |

| MDB1       | В   | psbsstl_8700 | Data 15 to 0 for SDRAM                               | 173 |          |  |

| MDB2       | В   | psbsstl_8700 | Data 15 to 0 for SDRAM                               | 172 |          |  |

| MDB3       | В   | psbsstl_8700 | Data 15 to 0 for SDRAM                               | 171 |          |  |

| MDB4       | В   | psbsstl_8700 | Data 15 to 0 for SDRAM                               | 170 |          |  |

| MDB5       | В   | psbsstl_8700 | Data 15 to 0 for SDRAM                               | 169 |          |  |

| MDB6       | В   | psbsstl_8700 | Data 15 to 0 for SDRAM                               | 168 |          |  |

| MDB7       | В   | psbsstl_8700 | Data 15 to 0 for SDRAM                               | 167 |          |  |

| MDB8       | В   | psbsstl_8700 | Data 15 to 0 for SDRAM                               | 164 |          |  |

| MDB9       | В   | psbsstl_8700 | Data 15 to 0 for SDRAM                               | 163 |          |  |

| MDB10      | В   | psbsstl_8700 | Data 15 to 0 for SDRAM                               | 162 |          |  |

| MDB11      | В   | psbsstl_8700 | Data 15 to 0 for SDRAM                               | 161 |          |  |

| MDB12      | В   | psbsstl_8700 | Data 15 to 0 for SDRAM                               | 160 |          |  |

| MDB13      | В   | psbsstl_8700 | Data 15 to 0 for SDRAM                               | 159 |          |  |

| MDB14      | В   | psbsstl_8700 | Data 15 to 0 for SDRAM                               | 158 |          |  |

| MDB15      | В   | psbsstl_8700 | Data 15 to 0 for SDRAM                               | 157 |          |  |

| USB        |     |              |                                                      |     | 1        |  |

| VDDA33T1   | Р   | vdd33th_abb  | Transceiver supply                                   | 191 | T        |  |

| VSSA33T2   | Р   | vssbbh_abb   | Transceiver supply                                   | 192 |          |  |

| DP         | В   | phtoa_abb    | Data pin (special pad , single-in-line <b>)</b>      | 193 |          |  |

| VSSA33T3   | Р   | vssbbh_abb   | Transceiver supply                                   | 194 |          |  |

| DM         | В   | phtoa_abb    | Data pin (special pad , single-in-line <b>)</b>      | 195 |          |  |

| VSSA33T4   | Р   | vssbbh_abb   | Transceiver supply                                   | 196 |          |  |

| VDDA33T5   | P   | vdd33th_abb  | Transceiver supply                                   | 197 |          |  |

| REXT       | 0   | phoarext_abb | analog signal (special pad , single-in-line <b>)</b> | 198 |          |  |

| VDDA33C6   | Р   | vdd33th_abb  | Common supply                                        | 199 |          |  |

| VSSA33C7   | Р   | vssbbh_abb   | Common supply                                        |     | <u> </u> |  |

| USBXO      | I   | phoa_abb     | X-tal out                                            | 201 | 1        |  |

| USBXI      | I   | phoa_abb     | X-tal in                                             | 202 | <u> </u> |  |

| ANALOGTEST | 0   | phoa_abb     | Analog Test in/out                                   | 203 | <u> </u> |  |

| VBUS       | I   | phtic        | USB2.0 Power detect / ext int 8                      | 45  | <u>†</u> |  |

Table 1-1. S5L8700X Pin Descriptions (Continued)

| Pin Name I/O     |            | Туре     | Pin Description                           | Pin | ETC |

|------------------|------------|----------|-------------------------------------------|-----|-----|

| FMC/ MMC/ MS/ AT | API/LCD if |          |                                           |     | 1   |

| HD0              | В          | pvbct8cd | P2.0/ATAPI HD0/LCDif D0/MSD/SMC IO0       | 175 |     |

| HD1              | В          | pvbct8cd | P2.1/ATAPI HD1/LCDif D1/ - /SMC IO1       | 176 |     |

| HD2              | В          | pvbct8cd | P2.2/ATAPI HD2/LCDif D2/ - /SMC IO2       | 177 |     |

| HD3              | В          | pvbct8cd | P2.3/ATAPI HD3/LCDif D3/ - /SMC IO3       | 178 |     |

| HD4              | В          | pvbct8cd | P2.4/ATAPI HD4/LCDif D4/ - /SMC IO4       | 179 |     |

| HD5              | В          | pvbct8cd | P2.5/ATAPI HD5/LCDif D5/ - /SMC IO5       | 180 |     |

| HD6              | В          | pvbct8cd | P2.6/ATAPI HD6/LCDif D6/ - /SMC IO6       | 181 |     |

| HD7              | В          | pvbct8cd | P2.7/ATAPI HD7/LCDif D7/ - /SMC IO7       | 182 |     |

| HD8              | В          | pvbct8cd | P3.0/ATAPI HD8/LCDif D8/SDC D0/SMC IO8    | 187 |     |

| HD9              | В          | pvbct8cd | P3.1/ATAPI HD9/LCDif D9/ - /SMC IO9       | 188 |     |

| HD10             | В          | pvbct8cd | P3.2/ATAPI HD10/LCDif D10/SDC D2/SMC IO10 | 204 |     |

| HD11             | В          | pvbct8cd | P3.3/ATAPI HD11/LCDif D11/SDC D3/SMC1011  | 205 |     |

| HD12             | В          | pvbct8cd | P3.4/ATAPI HD12/LCDif D12/ -/SMC 1012     | 206 |     |

| HD13             | В          | pvbct8cd | P3.5/ATAPI HD13/LCDif D13/SDC WP/SMC 1013 | 207 |     |

| HD14             | В          | pvbct8cd | P3.6/ATAPI HD14/LCDif D14/ - /SMC IO14    | 208 |     |

| HD15             | В          | pvbct8cd | P3.7/ATAPI HD15/LCDif D15/ - /SMC IO15    | 209 |     |

| CBLID            | В          | pvbct8cd | P4.0/ATAPI (BLID/ - / - / -               | 210 |     |

| DMACK            | В          | pvbct8cd | P4.1/ATAPLDMACK/LCDif REG/ - / SMC CLE    | 211 |     |

| DMARQ            | В          | pvbct8cd | P4.2/ATAPI DMARQ/ - / - / -               | 212 |     |

| IORDY            | В          | pvbct8cd | P4.3/ATAPI IORDY/ - / - / -               | 213 |     |

| DIOW             | В          | pvbct8cd | P4.4/ATAPI DIOW/LCDif nWR/MS BS/SMC nWR   | 214 |     |

| DIOR             | В          | pvbct8cd | P4.5/ATAPI DIOR/LCDif nRD/ - /SMC nRD     | 215 |     |

| ATA_RESET        | В          | pvbct8cd | P4.6/ATAPI RESET/ - / - /SMC nWP          | 216 |     |

| ATA_INTRQ        | В          | pvbct8cd | P4.7/ATAPI INTRQ/ - / - / -               | 217 |     |

| DA0              | В          | pvbct8cd | P5.0/ATAPI DA0/ - / - / -                 | 218 |     |

| DA1              | В          | pvbct8cd | P5.1/ATAPI DA1/ - / - / -                 | 219 |     |

| DA2              | В          | pvbct8cd | P5.2/ATAPI DA2/ - / - / -                 | 220 |     |

| CS0              | В          | pvbct8cd | P5.3/ATAPI CS0/ - / - / -                 | 221 | 1   |

| CS1              | В          | pvbct8cd | P5.4/ATAPI CS1/ - / - / -                 | 222 |     |

| VDEN             | В          | phbct4   | P5.5/VDEN                                 | 47  | 1   |

| VSYND            | В          | phbct4   | P5.6/VSYNC / SDC CMD                      | 48  |     |

| HSYNC            | В          | phbct4   | P5.7/HSYNC / SDC D1                       | 49  |     |

| Pin Name             | I/O            | Туре     | Pin Description                             | Pin | ETC |

|----------------------|----------------|----------|---------------------------------------------|-----|-----|

| nSMRDY               | В              | pvbct8cd | P6.0/SMC Ready & Busy state input/SMBUSY    | 225 |     |

| nSMCS0               | В              | pvbct8cd | P6.1/nNFCS0                                 | 226 |     |

| nSMCS1               | В              | pvbct8cd | P6.2/nNFCS1                                 | 227 | 1   |

| nSMCS2               | В              | pvbct8cd | P6.3/nNFCS2 / TxD1 (Uart1)                  | 228 | 1   |

| nSMCS3               | В              | pvbct8cd | P6.4/nNFCS3 / RxD1 (Uart1)                  | 229 | 1   |

| SDMMCLK              | В              | pvbct8cd | P6.5/SDCLK and MMCLK                        | 230 | 1   |

| MSCLK                | В              | pvbct8cd | P6.6/MS clock                               | 231 |     |

| ALE                  | В              | pvbct8cd | P6.7/SMC ALE                                | 232 | 1   |

| LCDnRST              | В              | phbct4   | P7.0/LCDif nRST/ VCLK                       | 2   | 1   |

| LCDnCS               | В              | phbct4   | P7.1/LCDif nCS                              | 6   |     |

| Ext interrupt / GPIO |                |          |                                             |     |     |

| P1_0                 | В              | phbct4   | P1.0 / ext int 0                            | 32  | Γ   |

| P1_1                 | В              | phbct4   | P1.1 / ext int 1                            | 33  | 1   |

| P1_2                 | В              | phbct4   | P1.2 / ext int 2                            | 34  | 1   |

| IIS                  |                |          |                                             | •   |     |

| IISMCK               | O(t)           | phbct4   | SAIU mater clock(WM8731L20 XTI/MCLK) / P7.2 | 8   | Τ   |

| IISWS                | O(t)           | phbct4   | SAIU word select(WM8731L20 DACLRC) / P7.3   | 10  |     |

| IISBCLK              | O(t)           | phbct4   | SAIU bit clock(WM8731L20 BCLK) / P7.4       | 12  |     |

| IISD_OUT             | O(t)           | phbct4   | SAIU data out(WM8731L20 DACDAT) / P7.5      | 16  | 1   |

| IISD_IN              | В              | phbct4   | SAIU data in(WM8732L20 ADCDATA) / P7.6      | 18  |     |

| SPDIF OUT            |                |          |                                             |     |     |

| SPDIFOUT             | ₿.             | phbct4   | SPDIF out / P7.7                            | 20  | Τ   |

| IIC                  |                |          |                                             |     | -   |

| IICCLK               | B(OD)          | phtbcd4  | IIC clock / WM8731L20 SCLK / P10.0          | 41  |     |

| IICDAT               | B(OD)          | phtbcd4  | IIC data / WM8731L20 SDIN / P10.1           | 43  | 1   |

| SP                   | - <del>4</del> |          |                                             |     |     |

Table 1-1. S5L8700X Pin Descriptions (Continued)

| Table 1-1. | S5L8700X | Pin Descri | ptions | (Continued) |

|------------|----------|------------|--------|-------------|

|------------|----------|------------|--------|-------------|

| Pin Name            | I/O | Туре        | Pin Description                          | Pin | ETC |

|---------------------|-----|-------------|------------------------------------------|-----|-----|

| TIMER & SPI         |     |             | - <b>I</b>                               |     |     |

| P0_0                | В   | phbct4      | P0.0 / TAOUT / nSSI                      | 24  | 1   |

| P0_1                | В   | phbct4      | P0.1/ TBOUT / SPICLK                     | 25  |     |

| P0_2                | В   | phbct4      | P0.2/ TCOUT / MOSI                       | 26  |     |

| P0_3                | В   | phbct4      | P0.3/ TDOUT / MISO                       | 27  |     |

| P0_4                | В   | phbct4      | P0.4/ TEXTCLK / pll0 out for test        | 28  |     |

| P0_5                | В   | phbct4      | P0.5/ TCAP / pll1 out for test           | 29  |     |

| UART                |     |             |                                          |     | 1   |

| P0_6                | В   | phbct4      | P0.6/ UART0 transmit pin / IISD1_OUT     | 30  |     |

| P0_7                | В   | phbct4      | P0.7/ UART0 receive pin / IISD2_OUT      | 31  |     |

| ADC                 | -   |             |                                          |     |     |

| ADC_VSSA            | P   | vssbbh_abb  | ADC agnd,avss33a1,avbb33a1,avss33a2      | 116 |     |

| ADC_VCC             | Р   | vdd33th_abb | ADC VREF,AVDD33A1,AVDD33A2 연결            | 115 |     |

| ADC0                | I   | phiar50_abb | 10-bit ADC input channel 0               | 114 |     |

| ADC1                | I   | phiar50_abb | 10-bit ADC input channel 1               | 113 |     |

| ADC2                | I   | phiar50_abb | 10-bit ADC input channel 2               | 112 |     |

| ADC3                | I   | phiar50_abb | 10-bit ADC input channel 3               | 111 |     |

| Digital Power & GNI | D   |             |                                          |     |     |

| Digital Power       | Р   | vdd12ih     | 15, 40, 78, 98, 125, 151, 183            | -   |     |

| Digital GND         | Р   | vssiph      | 16, 41, 79, 99, 126, 152, 184            | -   |     |

| USB 2.0 PHY         | Р   | vdd12ih     | 190                                      | -   |     |

| USB 2.0 PHY         | P   | vssiph      | 189                                      | -   |     |

| PAD Power * GND     |     |             | ·                                        |     |     |

| PAD Power 1         | Р   | vdd33oph    | 19, 44, 185, 223                         | -   |     |

| PAD GND 1           | P   | vssoh       | 20, 45, 186, 224                         | -   |     |

| PAD Power 2         | Р   | vdd33oph    | 80, 100 ( For NOR I/O ) * 2              | -   | 1   |

| PAD GND 2           | Р   | vssoh       | 81, 101 ( For NOR I/O ) * 2              | -   | 1   |

| PAD Power 3         | Р   | vdd33oph    | 127, 140, 153, 165 ( For SDRAM I/O ) * 4 | -   |     |

| PAD GND 3           | Р   | vssoh       | 128, 141, 154, 166 ( For SDRAM I/O ) * 4 | -   |     |

# PRODUCT OVERVIEW

# I/O BALL MAP

| Table 1-2. | S5L8700X I/C | BALL MAP |

|------------|--------------|----------|

|            |              |          |

|   | Ball<br>map | core pin<br>number | Pin<br>Assignment | Ball<br>map | core pin<br>number | Pin<br>Assignment | Ball<br>map | core pin<br>number | Pin<br>Assignment |   |

|---|-------------|--------------------|-------------------|-------------|--------------------|-------------------|-------------|--------------------|-------------------|---|

|   | B1          | 1                  | TEST              | R2          | 52                 | nSCS0             | R12         | 103                | CP0               |   |

|   | C2          | 2                  | LCDnRST           | T1          | 53                 | nSCS1             | U13         | 104                | PLL0_VSSBBA       |   |

|   | E4          | 3                  | BOOT_MODE         | P3          | 54                 | nSCS2             | V14         | 105                | PLL1_VDDA         |   |

|   | D3          | 4                  | nRESET            | P4          | 55                 | SDA0              | T13         | 106                | CP1               |   |

|   | E3          | 5                  | nARM_ADM          | R3          | 56                 | SDA1              | R13         | 107                | PLL1_VSSBBA       |   |

|   | C1          | 6                  | LCDnCS            | T2          | 57                 | SDA2              | U14         | 108                | PLL_VBBD          |   |

|   | D2          | 7                  | nTRST_DBG         | U1          | 58                 | SDA3              | V15         | 109                | PLL_VSSD          |   |

|   | D1          | 8                  | IISMCK            | V2          | 59                 | SDA4              | T14         | 110                | PLL_VDDD          |   |

|   | E2          | 9                  | TCK_DBG           | U3          | 60                 | SDA5              | R14         | 111                | ADC3              |   |

|   | F4          | 10                 | IISWS             | T4          | 61                 | SDA6              | V16         | 112                | ADC2              |   |

|   | E1          | 11                 | TMS_DBG           | R5          | 62                 | SDA7              | U15         | 113                | ADC1              |   |

|   | G5          | 12                 | IISBCLK           | R6          | 63                 | SDA8              | T15         | 114                | ADC0              |   |

|   | F3          | 13                 | TDI_DBG           | V3          | 64                 | SDA9              | U16         | 115                | ADC_VCC           |   |

|   | F2          | 14                 | TDO_DBG           | P7          | 65                 | SDA10             | V17         | 116                | ADC_VSSA          |   |

|   | F1          | 15                 | VDDI0             | U4          | 66                 | SDA11             | U18         | 117                | MDA9              |   |

|   | G4          | 16                 | IISD_OUT          | T5          | 67                 | SDA12             | T17         | 118                | MDA5              |   |

|   | H5          | 17                 | VSSI0             | V4          | 68                 | SDA13             | R16         | 119                | MDA4              |   |

|   | G3          | 18                 | IISD_IN           | R7          | 69                 | SDA14             | P15         | 120                | MDA8              |   |

|   | G1          | 19                 | VDDE0             | U5          | 70                 | SDA15             | T18         | 121                | MDA7              |   |

|   | G2          | 20                 | SPDIFOut          | V5          | 71                 | SDA16             | P16         | 122                | MDA11             |   |

|   | H4          | 21                 | VSSE0             | T6          | 72                 | SDA17             | B17         | 123                | MDA6              |   |

|   | H2          | 22                 | XI                | P8          | 73                 | SDA18             | R18         | 124                | MDA12             |   |

|   | H1          | 23                 | XO                | U6          | 74                 | SDA19             | M14         | 125                | VDDI4             |   |

|   | H3          | 24                 | P0_0              | V6          | 75                 | SDA20             | N15         | 126                | VSSI4             |   |

|   | J5          | 25                 | P0_1              | T7          | 76                 | SDA21             | M15         | 127                | VDDE4             |   |

|   | J4          | 26                 | P0_2              | P9          | 77                 | SDA22             | P18         | 128                | VSSE4             |   |

|   | J1          | 27                 | P0_3              | U7          | 78                 | VDDI2             | P17         | 129                | MDAB0             |   |

|   | J2          | 28                 | P0_4              | V7          | 79                 | VSSI2             | N16         | 130                | MDAB1             |   |

|   | JЗ          | 29                 | P0_5              | R8          | 80                 | VDDE2             | L14         | 131                | MDA10             |   |

|   | K1          | - 30               | P0_6              | T8          | 81                 | VSSE2             | N18         | 132                | MDA0              |   |

|   | K5          | 31                 | P0_7              | U8          | 82                 | SDB0              | N17         | 133                | MDA1              |   |

|   | K4          | 32                 | P1_0              | V8          | 83                 | SDB1              | M16         | 134                | MDA2              |   |

|   | K2          | 33                 | P1_1              | R9          | 84                 | SDB2              | M17         | 135                | MDA3              |   |

|   | 1           | 34                 | P1_2              | Т9          | 85                 | SDB3              | M18         | 136                | DCLK2             |   |

|   | K3 )        | 35                 | P1_3              | V9          | 86                 | SDB4              | L15         | 137                | nDCS0             |   |

|   | L5          | 36                 | P1_4              | U9          | 87                 | SDB5              | L16         | 138                | nDCS1             |   |

|   | L2          | 37                 | P1_5              | P10         | 88                 | SDB6              | L18         | 139                | nDCS2             |   |

| * | M1          | 38                 | P1_6              | R10         | 89                 | SDB7              | L17         | 140                | VDDE8             |   |

|   | L4          | 39                 | P1_7              | V10         | 90                 | SDB8              | K14         | 141                | VSSE8             |   |

|   | L3          | 40                 | VDDI1             | T10         | 91                 | SDB9              | K18         | 142                | DQS0              |   |

|   | N1          | 41                 | IICCLK            | U10         | 92                 | SDB10             | K17         | 143                | DQS1              |   |

|   | M2          | 42                 | VSSI1             | P11         | 93                 | SDB11             | K16         | 144                | DCLK              |   |

|   | M3          | 43                 | IICDAT            | V11         | 94                 | SDB12             | J16         | 145                | DCLKN             | l |

|   | N2          | 44                 | VDDE1             | U11         | 95                 | SDB13             | J18         | 146                | VREF              | l |

|   | P1          | 45                 | VBUS              | T11         | 96                 | SDB14             | K15         | 147                | DCKE              | l |

|   | M4          | 46                 | VSSE1             | R11         | 97                 | SDB15             | J15         | 148                | nRAS              | I |

|   | M5          | 47                 | VDEN              | V12         | 98                 | VDDI3             | H18         | 149                | nCAS              | l |

|   | P2          | 48                 | VSYNC             | P12         | 99                 | VSSI3             | J14         | 150                | nDWE              | I |

|   | R1          | 49                 | HSYNC             | U12         | 100                | VDDE3             | J17         | 151                | VDDI5             | l |

|   | N3          | 50                 | nSOE              | V13         | 101                | VSSE3             | H15         | 152                | VSSI5             | l |

|   | N4          | 51                 | nSWE              | T12         | 102                | PLL0_VDDA         | G18         | 153                | VDDE5             |   |

| Ball | core pin | Pin        | Ball | core pin | Pin        | Ball | core pin | Pin        |

|------|----------|------------|------|----------|------------|------|----------|------------|

| map  | number   | Assignment | map  | number   | Assignment | map  | number   | Assignment |

| H14  | 154      | VSSE5      | A15  | 181      | HD6        | B8   | 208      | HD14       |

| H17  | 155      | DQM1       | D14  | 182      | HD7        | C9   | 209      | HD15       |

| H16  | 156      | DQM0       | D13  | 183      | VDDI6      | A8   | 210      | CBLID      |

| F18  | 157      | MDB15      | E12  | 184      | VSSI6      | D8   | 211      | DMACK      |

| G15  | 158      | MDB14      | A14  | 185      | VDDE6      | C8   | 212      | DMARQ      |

| G17  | 159      | MDB13      | B14  | 186      | VSSE6      | B7   | 213      | IORDY      |

| G14  | 160      | MDB12      | C13  | 187      | HD8        | A7   | 214      | DIOW       |

| E18  | 161      | MDB11      | B13  | 188      | HD9        | E8   | 215      | DIOR       |

| G16  | 162      | MDB10      | A13  | 189      | VSSI7      | D7   | 216      | ATA_RESET  |

| F17  | 163      | MDB9       | D12  | 190      | VDDI7      | A6   | 217      | ATA_INTRQ  |

| D18  | 164      | MDB8       | E11  | 191      | VDDA33T1   | B6   | 218      | DA0        |

| F15  | 165      | VDDE9      | C12  | 192      | VSSA33T2   | C7   | 219      | DA1        |

| F16  | 166      | VSSE9      | A12  | 193      | DP         | E7   | 220      | DA2        |

| E17  | 167      | MDB7       | B12  | 194      | VSSA33T3   | A5   | 221      | CS0        |

| C18  | 168      | MDB6       | A11  | 195      | DM         | B5   | 222      | CS1        |

| E15  | 169      | MDB5       | B11  | 196      | VSSA33T4   | D6   | 223      | VDDE7      |

| E16  | 170      | MDB4       | D11  | 197      | VDDA33T5   | C6   | 224      | VSSE7      |

| D17  | 171      | MDB3       | C11  | 198      | REXT       | A4   | 225      | nSMRDY     |

| D16  | 172      | MDB2       | B10  | 199      | VDDA33C6   | B4   | 226      | nSMCS0     |

| C17  | 173      | MDB1       | D10  | 200      | VSSA33C7   | D5   | 227      | nSMCS1     |

| B18  | 174      | MDB0       | E10  | 201      | USBXO      | C5   | 228      | nSMCS2     |

| A17  | 175      | HD0        | A10  | 202      | USBXI      | A3   | 229      | nSMCS3     |

| A16  | 176      | HD1        | B9   | 203      | ANALOGTEST | C4   | 230      | SDMMCLK    |

| B16  | 177      | HD2        | C10  | 204      | HD10       | B3   | 231      | MSCLK      |

| B15  | 178      | HD3        | E9   | 205      | HD11       | A2   | 232      | ALE        |

| C15  | 179      | HD4        | A9   | 206      | HD12       |      |          |            |

| C14  | 180      | HD5        | D9   | 207      | HD13       |      |          |            |

|      |          |            | G    | C        | <b>3</b> × |      |          |            |

|      |          |            |      |          |            |      |          |            |

| P    |          | JUN        |      |          |            |      |          |            |

|      |          |            |      |          |            |      |          |            |

Table 1-2. S5L8700X I/O BALL MAP (Continued)

#### PRODUCT OVERVIEW

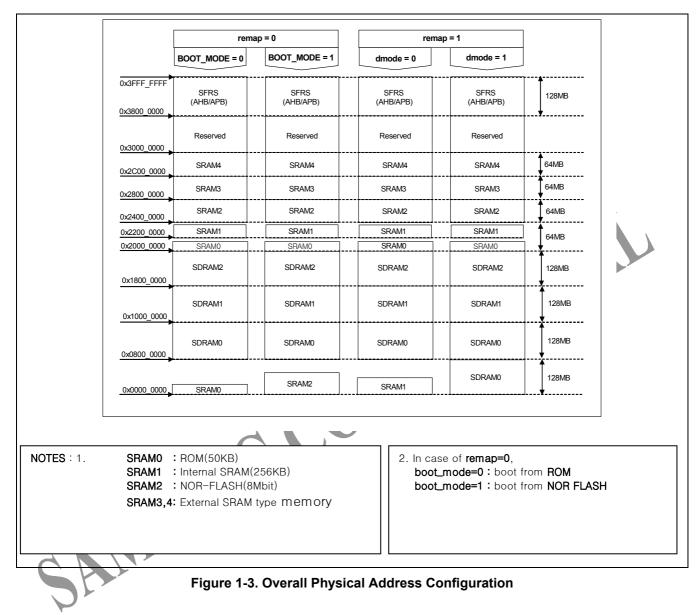

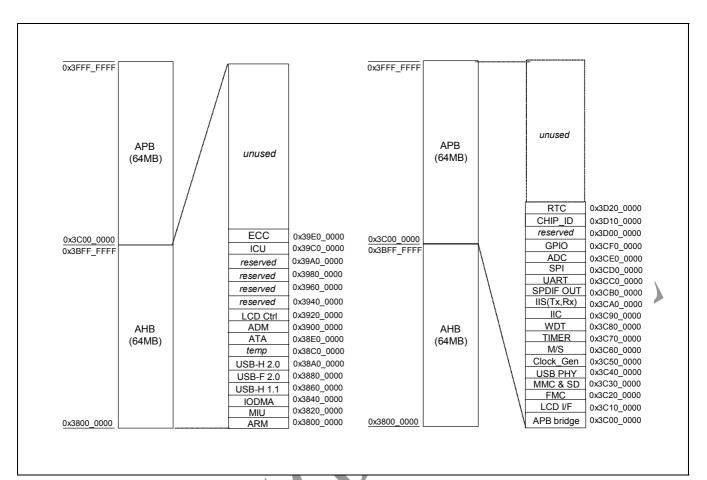

#### **MEMORY MAP**

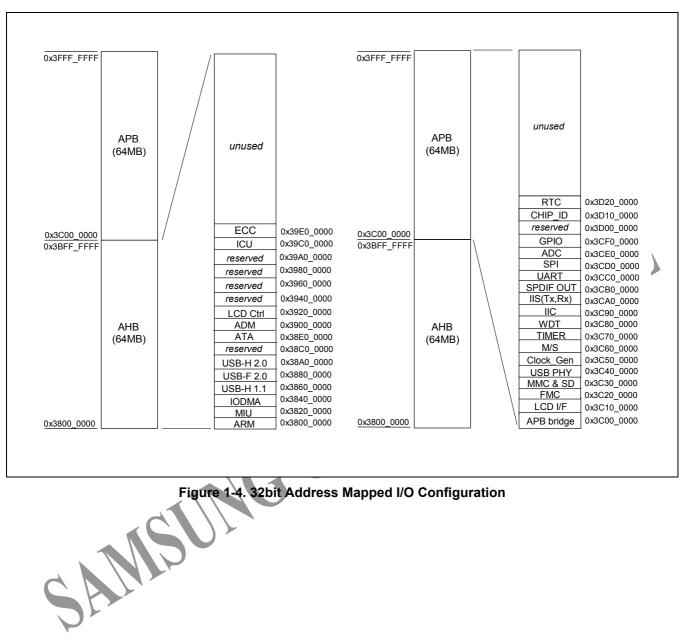

# Figure 1-4. 32bit Address Mapped I/O Configuration

NOTES

SAMSUNG CONTRIDUMINAL

# 2 PROGRAMMER'S MODEL

# **OVERVIEW**

S5L8700X was developed using the advanced ARM9TDMI core designed by advanced RISC machines, Ltd. — Processor Operating States

From the programmer's point of view, the ARM9TDMI can be in one of two states:

- ARM state which executes 32-bit, word-aligned ARM instructions.

- THUMB state which operates with 16-bit, half-word-aligned THUMB instructions. In this state, the PC uses bit 1 to select between alternate half-words.

# NOTE

Transition between these two states does not affect the processor mode or the contents of the registers.

#### Switching State

#### **Entering THUMB State**

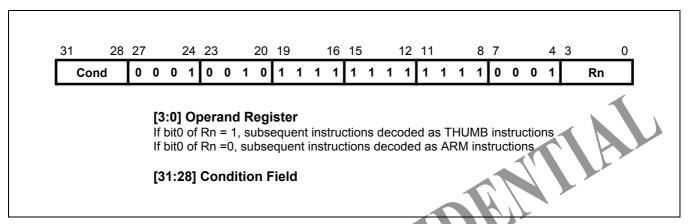

Entry into THUMB state can be achieved by executing a BX instruction with the state bit (bit 0) set in the operand register.

Transition to THUMB state will also occur automatically on return from an exception (IRQ, FIQ, UNDEF, ABORT, SWI etc.), if the exception was entered with the processor in THUMB state.

# Entering ARM State

Entry into ARM state happens:

- 1. On execution of the BX instruction with the state bit clear in the operand register.

- 2. On the processor taking an exception (IRQ, FIQ, RESET, UNDEF, ABORT, SWI etc.). In this case, the PC is placed in the exception mode's link register, and execution commences at the exception's vector address.

#### **Memory Formats**

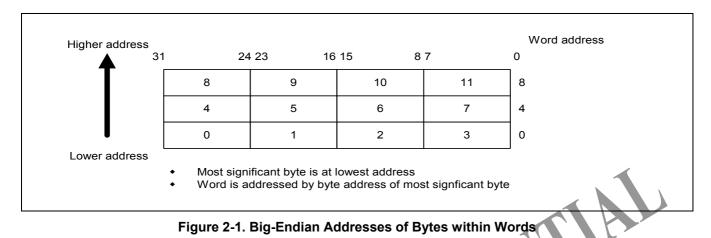

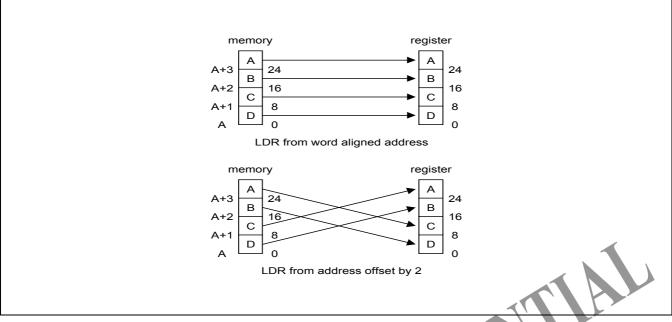

ARM9TDMI views memory as a linear collection of bytes numbered upwards from zero. Bytes 0 to 3 hold the first stored word, bytes 4 to 7 the second and so on. ARM9TDMI can treat words in memory as being stored either in Big-Endian or Little-Endian format.

# **BIG-ENDIAN FORMAT**

In Big-Endian format, the most significant byte of a word is stored at the lowest numbered byte and the least significant byte at the highest numbered byte. Byte 0 of the memory system is therefore connected to data lines 31 through 24.

# NOTE

The data locations in the external memory are different with Figure 2-1 in the S5L8700X.

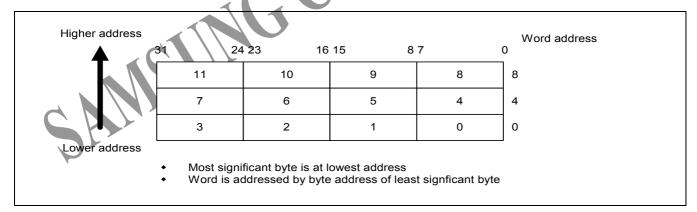

# LITTLE-ENDIAN FORMAT

In Little-Endian format, the lowest numbered byte in a word is considered the word's least significant byte, and the highest numbered byte the most significant. Byte 0 of the memory system is therefore connected to data lines 7 through 0.

Figure 2-2. Little-Endian Addresses of Bytes Words

# INSTRUCTION LENGTH

Instructions are either 32 bits long (in ARM state) or 16 bits long (in THUMB state). **Data Types**

ARM9TDMI supports byte (8-bit), half-word (16-bit) and word (32-bit) data types. Words must be aligned to fourbyte boundaries and half words to two-byte boundaries.

# **OPERATING MODES**

ARM9TDMI supports seven modes of operation:

- User (usr) : The normal ARM program execution state

- FIQ (fiq) : Designed to support a data transfer or channel process

- IRQ (irq) : Used for general-purpose interrupt handling

- Supervisor (svc) : Protected mode for the operating system

- Abort mode (abt) : Entered after a data or instruction prefetch abort

- System (sys) : A privileged user mode for the operating system

- Undefined (und) : Entered when an undefined instruction is executed

Mode changes may be made under software control, or may be brought about by external interrupts or exception processing. Most application programs will execute in User mode. The non-user modes known as privileged modes-are entered in order to service interrupts or exceptions, or to access protected resources. **REGISTERS**

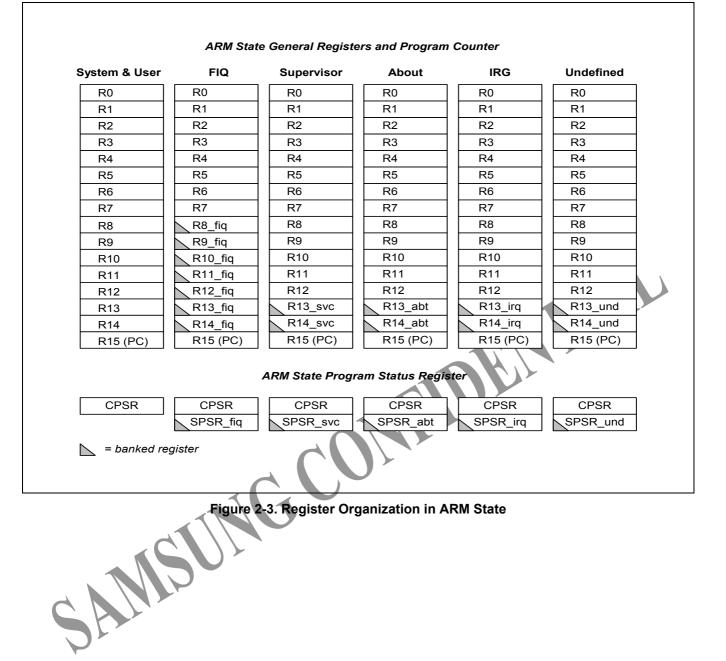

ARM9TDMI has a total of 37 registers-31 general-purpose 32-bit registers and six status registers - but these cannot all be seen at once. The processor state and operating mode dictate which registers are available to the programmer.

#### The ARM State Register Set

In ARM state, 16 general registers and one or two status registers are visible at any one time. In privileged (non-User) modes, mode-specific banked registers are switched in. Figure 2-3 shows which registers are available in each mode: the banked registers are marked with a shaded triangle.

The ARM state register set contains 16 directly accessible registers: R0 to R15. All of these except R15 are general-purpose, and may be used to hold either data or address values. In addition to these, there is a seventeenth register used to store status information.

0

Register 14

is used as the subroutine link register. This receives a copy of R15 when a branch and link (BL) instruction is executed. At all other times it may be treated as a general-purpose register. The corresponding banked registers R14\_svc, R14\_irq, R14\_fiq, R14\_abt and R14\_und are similarly used to hold the return values of R15 when interrupts and exceptions arise, or when branch and link instructions are executed within interrupt or exception routines.

Register

Register 16

holds the Program Counter (PC). In ARM state, bits [1:0] of R15 are zero and bits [31:2] contain the PC. In THUMB state, bit [0] is zero and bits [31:1] contain the PC. is the CPSR (Current Program Status Register). This contains condition code flags and the current mode bits.

FIQ mode has seven banked registers mapped to R8-14 (R8\_fiq-R14\_fiq). In ARM state, many FIQ handlers do not need to save any registers. User, IRQ, Supervisor, Abort and Undefined each have two banked registers mapped to R13 and R14, allowing each of these modes to have a private stack pointer and link registers.

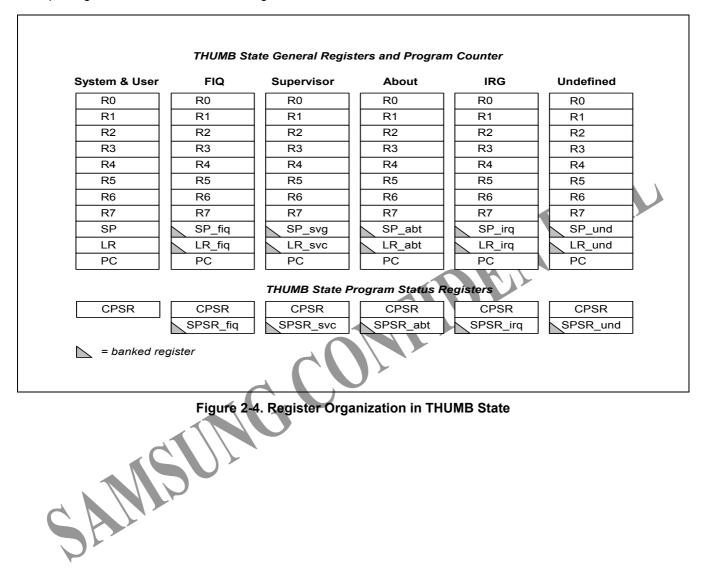

#### The THUMB State Register Set

The THUMB state register set is a subset of the ARM state set. The programmer has direct access to eight general registers, R0–R7, as well as the Program Counter (PC), a stack pointer register (SP), a link register (LR), and the CPSR. There are banked stack pointers, link registers and Saved Process Status Registers (SPSRs) for each privileged mode. This is shown in Figure 2-4.

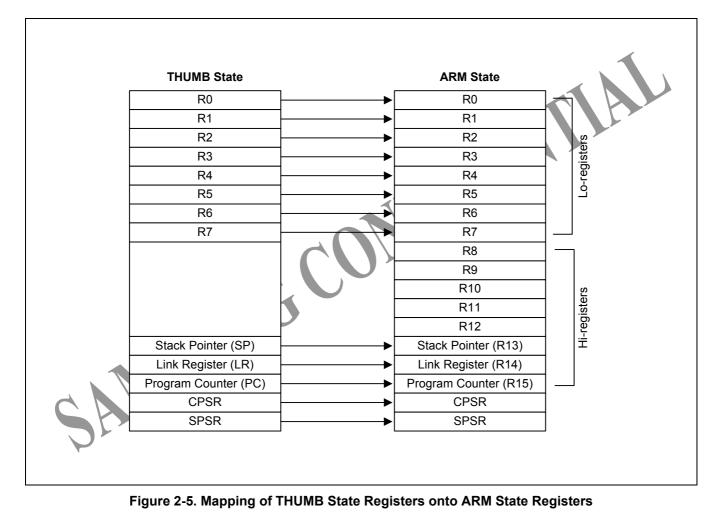

# THE RELATIONSHIP BETWEEN ARM AND THUMB STATE REGISTERS

The THUMB state registers relate to the ARM state registers in the following way:

- THUMB state R0–R7 and ARM state R0–R7 are identical

- THUMB state CPSR and SPSRs and ARM state CPSR and SPSRs are identical

- THUMB state SP maps onto ARM state R13

- THUMB state LR maps onto ARM state R14

- The THUMB state program counter maps onto the ARM state program counter (R15)

This relationship is shown in Figure 2-5.

#### Accessing Hi-Registers in THUMB State

In THUMB state, registers R8–R15 (the Hi registers) are not part of the standard register set. However, the assembly language programmer has limited access to them, and can use them for fast temporary storage.

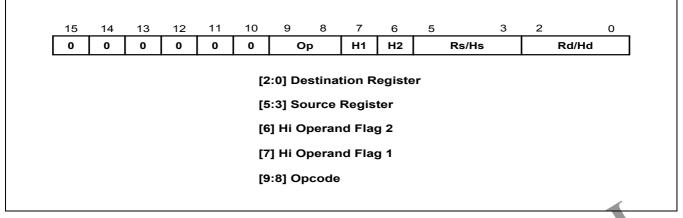

A value may be transferred from a register in the range R0-R7 (a Lo register) to a Hi register, and from a Hi register to a Lo register, using special variants of the MOV instruction. Hi register values can also be compared against or added to Lo register values with the CMP and ADD instructions. For more information, refer to Figure 3-34.

#### **The Program Status Registers**

The ARM9TDMI contains a Current Program Status Register (CPSR), plus five Saved Program Status Registers (SPSRs) for use by exception handlers. These register's functions are:

- Hold information about the most recently performed ALU operation

- Control the enabling and disabling of interrupts

- Set the processor operating mode •

|                                                                                                                                           | -         |        | -    | ting mo |    | ıre 2-6 | 6.   |     |   |   |   |       |         |    |    |    |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------|------|---------|----|---------|------|-----|---|---|---|-------|---------|----|----|----|

| Con                                                                                                                                       | idition ( | Code F | lags |         | (F | Reserve | ed)  |     |   |   | 1 | Contr | ol-Bits |    |    |    |

| 31                                                                                                                                        | 30        | 29     | 28   | 27      | 26 | 25      | 24   | , 8 | 7 | 6 | 5 | 4     | 3       | 2  | 1  | 0  |

| N                                                                                                                                         | z         | с      | v    |         |    |         | .//. |     | I | F | т | M4    | М3      | M2 | M1 | МО |

| N     Z     C     V     .     .     .     I     I     III     IIII     IIII     IIIII       Overflow     Overflow     Carry/Borrow/Extend |           |        |      |         |    |         |      |     |   |   |   |       |         |    |    |    |

| Figure 2-6. Program Status Register Format                                                                                                |           |        |      |         |    |         |      |     |   |   |   |       |         |    |    |    |

#### **The Condition Code Flags**

The N, Z, C and V bits are the condition code flags. These may be changed as a result of arithmetic and logical operations, and may be tested to determine whether an instruction should be executed. In ARM state, all instructions may be executed conditionally: see Table 3-2 for details.

In THUMB state, only the branch instruction is capable of conditional execution: see Figure 3-46 for details.

#### The Control Bits

The bottom 8 bits of a PSR (incorporating I, F, T and M[4:0]) are known collectively as the control bits. These will change when an exception arises. If the processor is operating in a privileged mode, they can also be manipulated by software.

The T bit

This reflects the operating state. When this bit is set, the processor is executing in THUMB state, otherwise it is executing in ARM state. This is reflected on the TBIT external signal.

Note that the software must never change the state of the TBIT in the CPSR. If this happens, the processor will enter an unpredictable state.

Interrupt disable bits The I and F bits are the interrupt disable bits. When set, these disable the IRQ and FIQ interrupts respectively.

The mode bits The M4, M3, M2, M1 and M0 bits (M[4:0]) are the mode bits. These determine the processor's operating mode, as shown in Table 2-1. Not all combinations of the mode bits define a valid processor mode. Only those explicitly described shall be used. The user should be aware that if any illegal value is programmed into the mode bits, M[4:0], then the processor will enter an unrecoverable state. If this occurs, reset should be applied.

| M[4:0] | Mode       | Visible THUMB State Registers | Visible ARM State Registers |

|--------|------------|-------------------------------|-----------------------------|

| 10000  | User       | R7R0,                         | R14R0,                      |

|        |            | LR, SP                        | PC, CPSR                    |

|        |            | PC, CPSR                      |                             |

| 10001  | FIQ        | R7R0,                         | R7R0,                       |

|        |            | LR_fiq, SP_fiq                | R14_fiqR8_fiq,              |

|        |            | PC, CPSR, SPSR_fiq            | PC, CPSR, SPSR_fiq          |

| 10010  | IRQ        | R7R0,                         | R12R0,                      |

|        |            | LR_irq, SP_irq                | R14_irqR13_irq,             |

|        |            | PC, CPSR, SPSR_irq            | PC, CPSR, SPSR_irq          |

| 10011  | Supervisor | R7R0,                         | R12R0,                      |

|        |            | LR_svc, SP_svc,               | R14_svcR13_svc,             |

|        |            | PC, CPSR, SPSR_svc            | PC, CPSR, SPSR_svc          |

| 10111  | Abort      | R7R0,                         | R12R0,                      |

|        |            | LR_abt, SP_abt,               | R14_abt,.R13_abt,           |

|        |            | PC, CPSR, SPSR_abt            | PC, CPSR, SPSR_abt          |

| 11011  | Undefined  | R7R0                          | R12R0,                      |

|        |            | LR_und, SP_und,               | R14_undR13_und,             |

|        |            | PC, CPSR, SPSR_und            | PC, CPSR                    |

| 11111  | System     | R7R0,                         | R14R0,                      |

|        |            | LR, SP                        | PC, CPSR                    |

|        |            | PC, CPSR                      |                             |

|        | •          |                               |                             |

| Table 2-1. | PSR | Mode | Bit | Values |

|------------|-----|------|-----|--------|

|------------|-----|------|-----|--------|

#### Reserved bits

The remaining bits in the PSRs are reserved. When changing a PSR's flag or control bits, you must ensure that these unused bits are not altered. Also, your program should not rely on them containing specific values, since in future processors they may read as one or zero.

# EXCEPTIONS

Exceptions arise whenever the normal flow of a program has to be halted temporarily, for example to service an interrupt from a peripheral. Before an exception can be handled, the current processor state must be preserved so that the original program can resume when the handler routine has finished.

It is possible for several exceptions to arise at the same time. If this happens, they are dealt with in a fixed order. See Exception Priorities on page 2-14.

#### Action on Entering an Exception

When handling an exception, the ARM9TDMI:

- Preserves the address of the next instruction in the appropriate Link Register. If the exception has been entered from ARM state, then the address of the next instruction is copied into the Link Register (that is, current PC + 4 or PC + 8 depending on the exception. See Table 2-2 on for details). If the exception has been entered from THUMB state, then the value written into the Link Register is the current PC offset by a value such that the program resumes from the correct place on return from the exception. This means that the exception handler need not determine which state the exception was entered from. For example, in the case of SWI, MOVS PC, R14\_svc will always return to the next instruction regardless of whether the SWI was executed in ARM or THUMB state.

- 2. Copies the CPSR into the appropriate SPSR

- 3. Forces the CPSR mode bits to a value which depends on the exception

- 4. Forces the PC to fetch the next instruction from the relevant exception vector

It may also set the interrupt disable flags to prevent otherwise unmanageable nesting of exceptions. If the processor is in THUMB state when an exception occurs, it will automatically switch into ARM state when the PC is loaded with the exception vector address.

#### Action on Leaving an Exception

On completion, the exception handler:

- 1. Moves the Link Register, minus an offset where appropriate, to the PC. (The offset will vary depending on the type of exception.)

- 2. Copies the SPSR back to the CRSR

- 3. Clears the interrupt disable flags, if they were set on entry

#### NOTE

An explicit switch back to THUMB state is never needed, since restoring the CPSR from the SPSR automatically sets the T bit to the value it held immediately prior to the exception.

#### **Exception Entry/Exit Summary**

Table 2-2 summarizes the PC value preserved in the relevant R14 on exception entry, and the recommended instruction for exiting the exception handler.

|       | Return Instruction   | Previo    | Notes       |   |

|-------|----------------------|-----------|-------------|---|

|       |                      | ARM R14_x | THUMB R14_x |   |

| BL    | MOV PC, R14          | PC + 4    | PC + 2      | 1 |

| SWI   | MOVS PC, R14_svc     | PC + 4    | PC + 2      | 1 |

| UDEF  | MOVS PC, R14_und     | PC + 4    | PC + 2      | 1 |

| FIQ   | SUBS PC, R14_fiq, #4 | PC + 4    | PC + 4      | 2 |

| IRQ   | SUBS PC, R14_irq, #4 | PC + 4    | PC + 4      | 2 |

| PABT  | SUBS PC, R14_abt, #4 | PC + 4    | PC + 4      | 1 |

| DABT  | SUBS PC, R14_abt, #8 | PC + 8    | PC + 8      | 3 |

| RESET | NA                   | _         |             | 4 |

| Table  | 2-2  | Excentio | n Entry/Exit |

|--------|------|----------|--------------|

| I abic | L-L. | LACOPLIO |              |

#### NOTES:

Where PC is the address of the BL/SWI/Undefined Instruction fetch which had the prefetch abort. 1.

Where PC is the address of the instruction which did not get executed since the FIQ or IRQ took priority. 2.

Where PC is the address of the Load or Store instruction which generated the data abort 3.

The value saved in R14 svc upon reset is unpredictable. 4

# FIQ

The FIQ (Fast Interrupt Request) exception is designed to support a data transfer or channel process, and in ARM state has sufficient private registers to remove the need for register saving (thus minimizing the overhead of context switching).

FIQ is externally generated by taking the nFIQ input LOW. This input can except either synchronous or asynchronous transitions, depending on the state of the ISYNC input signal. When ISYNC is LOW, nFIQ and nIRQ are considered asynchronous, and a cycle delay for synchronization is incurred before the interrupt can affect the processor flow.

Irrespective of whether the exception was entered from ARM or Thumb state, a FIQ handler should leave the interrupt by executing SUBS

PC,R14\_fiq,#4

FIQ may be disabled by setting the CPSR's F flag (but note that this is not possible from User mode). If the F flag is clear, ARM9TDMI checks for a LOW level on the output of the FIQ synchroniser at the end of each instruction.

# IRQ

The IRQ (Interrupt Request) exception is a normal interrupt caused by a LOW level on the nIRQ input. IRQ has a lower priority than FIQ and is masked out when a FIQ sequence is entered. It may be disabled at any time by setting the I bit in the CPSR, though this can only be done from a privileged (non-User) mode.

Irrespective of whether the exception was entered from ARM or Thumb state, an IRQ handler should return from the interrupt by executing

SUBS PC,R14 irg,#4

# Abort

An abort indicates that the current memory access cannot be completed. It can be signaled by the external ABORT input. ARM9TDMI checks for the abort exception during memory access cycles.

There are two types of abort:

- Prefetch abort: occurs during an instruction prefetch.

- Data abort: occurs during a data access.

If a prefetch abort occurs, the prefetched instruction is marked as invalid, but the exception will not be taken until the instruction reaches the head of the pipeline. If the instruction is not executed - for example because a branch occurs while it is in the pipeline - the abort does not take place.

If a data abort occurs, the action taken depends on the instruction type:

- Single data transfer instructions (LDR, STR) write back modified base registers; the Abort handler must be • aware of this.

- The swap instruction (SWP) is aborted as though it had not been executed.

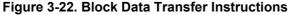

- Block data transfer instructions (LDM, STM) complete. If write-back is set, the base is updated. If the instruction would have overwritten the base with data (ie it has the base in the transfer list), the overwriting is prevented. All register overwriting is prevented after an abort is indicated, which means in particular that R15 (always the last register to be transferred) is preserved in an aborted LDM instruction.

The abort mechanism allows the implementation of a demand paged virtual memory system. In such a system the processor is allowed to generate arbitrary addresses. When the data at an address is unavailable, the Memory Management Unit (MMU) signals an abort. The abort handler must then work out the cause of the abort, make the requested data available, and retry the aborted instruction. The application program needs no knowledge of the amount of memory available to it, nor is its state in any way affected by the abort.

After fixing the reason for the abort, the handler should execute the following irrespective of the state (ARM or Thumb):

SUBS

SUBS

PC,R14 abt,#4 PC,R14 abt,#8

- for a prefetch abort, or ·

- for a data abort

This restores both the PC and the CPSR, and retries the aborted instruction.

#### Software Interrupt

The software interrupt instruction (SWI) is used for entering Supervisor mode, usually to request a particular supervisor function. A SWI handler should return by executing the following irrespective of the state (ARM or Thumb):

MOV PC,R14\_svc

This restores the PC and CPSR, and returns to the instruction following the SWI.

NOTE

nFIQ, nIRQ, ISYNC, LOCK, BIGEND, and ABORT pins exist only in the ARM9TDMI CPU core.

#### **Undefined Instruction**

When ARM9TDMI comes across an instruction which it cannot handle, it takes the undefined instruction trap. This mechanism may be used to extend either the THUMB or ARM instruction set by software emulation. After emulating the failed instruction, the trap handler should execute the following irrespective of the state (ARM or Thumb):

MOVS PC,R14\_und

This restores the CPSR and returns to the instruction following the undefined instruction.

#### **Exception Vectors**

The following table shows the exception vector addresses.

| Table 2-3. | <b>Exception Vectors</b> |

|------------|--------------------------|

|------------|--------------------------|

| Address    | Exception             | Mode in Entry |

|------------|-----------------------|---------------|

| 0x00000000 | Reset                 | Supervisor    |

| 0x0000004  | Undefined instruction | Undefined     |

| 0x0000008  | Software Interrupt    | Supervisor    |

| 0x000000C  | Abort (prefetch)      | Abort         |

| 0x00000010 | Abort (data)          | Abort         |

| 0x00000014 | Reserved              | Reserved      |

| 0x00000018 | IRQ                   | IRQ           |

| 0x0000001C | FIQ                   | FIQ           |

# **Exception Priorities**

When multiple exceptions arise at the same time, a fixed priority system determines the order in which they are handled:

Highest priority:

- 1. Reset

- 2. Data abort

- 3. FIQ

- 4. IRQ

- 5. Prefetch abort

Lowest priority:

6. Undefined Instruction, Software interrupt.

# Not All Exceptions Can Occur at Once:

Undefined Instruction and Software Interrupt are mutually exclusive, since they each correspond to particular (non-overlapping) decoding of the current instruction.

If a data abort occurs at the same time as a FIQ, and FIQs are enabled (ie the CPSR's F flag is clean), ARM9TDMI enters the data abort handler and then immediately proceeds to the FIQ vector. A normal return from FIQ will cause the data abort handler to resume execution. Placing data abort at a higher priority than FIQ is necessary to ensure that the transfer error does not escape detection. The time for this exception entry should be added to worst-case FIQ latency calculations.

#### **INTERRUPT LATENCIES**

The worst case latency for FIQ, assuming that it is enabled, consists of the longest time the request can take to pass through the synchroniser (Tsyncmax if asynchronous), plus the time for the longest instruction to complete (Tldm, the longest instruction is an LDM which loads all the registers including the PC), plus the time for the data abort entry (Texc), plus the time for FIQ entry (Tfig). At the end of this time ARM9TDMI will be executing the instruction at 0x1C.

Tsyncmax is 3 processor cycles, Tldm is 20 cycles, Texc is 3 cycles, and Tfig is 2 cycles. The total time is therefore 28 processor cycles. This is just over 1.4 microseconds in a system which uses a continuous 20 MHz processor clock. The maximum IRQ latency calculation is similar, but must allow for the fact that FIQ has higher priority and could delay entry into the IRQ handling routine for an arbitrary length of time. The minimum latency for FIQ or IRQ consists of the shortest time the request can take through the synchroniser (Tsyncmin) plus Tfig. This is 4 processor cycles.

#### Reset

When the nRESET signal goes LOW, ARM9TDMI abandons the executing instruction and then continues to fetch instructions from incrementing word addresses.

When nRESET goes HIGH again, ARM9TDMI:

- 1. Overwrites R14 svc and SPSR svc by copying the current values of the PC and CPSR into them. The value of the saved PC and SPSR is not defined.

- 2. Forces M[4:0] to 10011 (Supervisor mode), sets the I and F bits in the CPSR, and clears the CPSR's T bit.

- 3. Forces the PC to fetch the next instruction from address 0x00.

- Execution resumes in ARM state. 4.

# **INTRODUCTION FOR ARM940T**

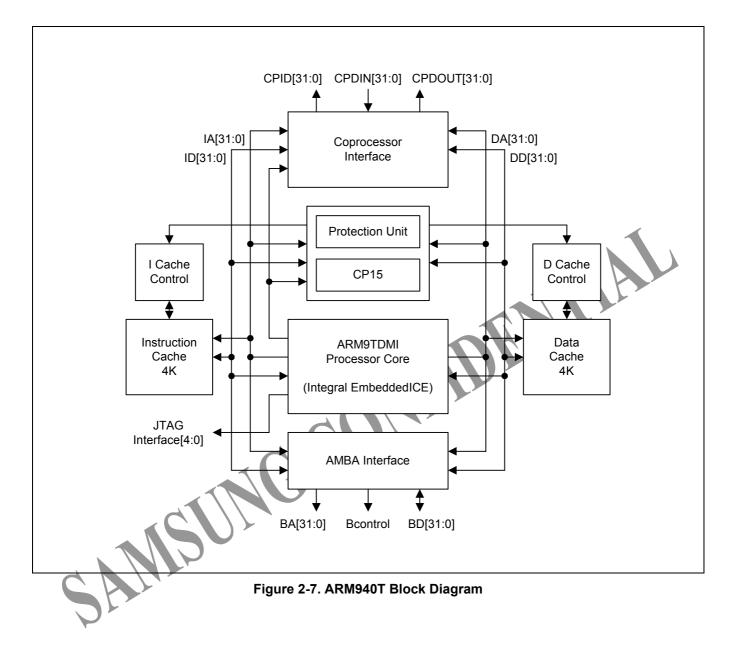

The ARM940T cached processor macrocell is a member of the ARM9 Thumb Family of high-performance 32-bit system-on-a-chip processor solutions. It is targeted at a wide range of embedded control applications where high performance, low system cost, small die size, and low power are key considerations.

The ARM940T processor macrocell provides a complete high performance CPU subsystem, including ARM9TDMI RISC integer CPU, caches, write buffer, and protection unit, with an AMBA ASB bus interface. Providing a complete high-frequency CPU subsystem frees the system-on-a-chip designer to concentrate on design issues unique to their system.

The ARM9TDMI core within the ARM940T macrocell executes both the 32-bit ARM and 16-bit Thumb instruction sets, allowing the user to trade off between high performance and high code density. It is binary compatible with ARM7TDMI, ARM10TDMI, and StrongARM processors, and is supported by a wide range of tools, operating systems, and application software.

The ARM940T processor macrocell is designed to be integrated into larger chips. It supports EmbeddedICE software and hardware debug and efficient production test when embedded in larger devices. The Advanced Microcontroller Bus Architecture (AMBA) provides a high performance 32-bit System Bus (ASB) and a low power peripheral bus (APB). The ASB is re-used to provide a channel for production test vectors with low silicon and pin overhead. The ASB is a multi-master on-chip bus interface designed specifically to address the needs of system-on-a-chip designs.

The EmbeddedICE software and hardware debug features of the ARM940T macrocell are accessed via a standard 5-pin JTAG port, and are supported by ARM's Software Development Toolkit and Multi-ICE interface hardware. The EmbeddedICE features allow software download and debug of the final production system with no cost overhead (there is no monitor code or other use of target resident RAM or ROM). The ARM940T processor has a Harvard cache architecture with separate 4KB instruction and 4KB data caches,

The ARM940T processor has a Harvard cache architecture with separate 4KB instruction and 4KB data caches, each with a 4-word line length. A protection unit allows 8 regions of memory to be defined, each with individual cache and write buffer configurations and access permissions. The cache system is software configurable to provide highest average performance or to meet the needs of real-time systems.

Software configurable options include:

- Random or round robin replacement algorithm

- Write-through or write-back cache operation (independently selectable for each memory region)

- Cache locking with granularity 1/64 th of cache size.

Overall, the cache and write buffers improve CPU performance and minimize accesses to the AMBA bus and to any off-chip memory, thus reducing overall system power consumption.

The ARM940T includes support for coprocessors, allowing a floating point unit or other application specific hardware acceleration to be added.

To minimize die size and power consumption the ARM940T does not provide virtual to physical address mapping as this is not required in most embedded applications. For systems requiring virtual memory capability, ARM provides an alternative product, the ARM920T cached processor macrocell. The ARM940T also features a TrackingICE mode which allows an approach similar to a conventional ICE mode of operation.

# ARM940T BLOCK DIAGRAM

# ABOUT THE ARM940T PROGRAMMER'S MODEL

The ARM940T cached processor macrocell includes the ARM9TDMI microprocessor core, instruction and data caches, a write-buffer, and a protection unit for defining the attributes of regions of memory. The ARM940T incorporates two coprocessors:

- CP14 which allows software access to the debug communications channel

- CP15 which allows configuration of the caches, protection unit, and other system options such as big or little endian operation.

The ARM940T also features an external coprocessor interface which allows the attachment of a closely coupled coprocessor on the same chip, for example, a floating point unit.

The programmer's model of the ARM940T consists of the programmer's model of the ARM9TDMI (see About the ARM9TDMI programmer's model on page 2-3) with the following additions and modifications:

- Memory accesses for instruction fetches and data loads and stores may be cached or buffered. Cache and write buffer configuration and operation is described in detail in following chapters.

- The registers defined in CP14 are accessible with MCR and MRC instructions. These are described in Debug communications channel on page 8-46.

- The registers defined in CP15 are accessible with MCR and MRC instructions. These are described in ARM940T CP15 registers on page 2-5.

- Registers and operations provided by any coprocessors attached to the external coprocessor interface will be accessible with appropriate coprocessor instructions.

The ARM9TDMI processor core implements ARM Architecture v4T, and so executes the ARM 32-bit instruction set and the compressed Thumb 16-bit instruction set. The programmer's model is fully described in the ARM Architecture Reference Manual.

The ARM v4T architecture specifies a small number of implementation options. The options selected in the ARM9TDMI implementation are listed in Table 2-4. For comparison, the options selected for the ARM9TDMI implementation are also shown.

| Processor Core ARM<br>Architecture | Data Abort Mode | Value Stored by Direct<br>STR, STRT, STM of PC |

|------------------------------------|-----------------|------------------------------------------------|

| ARM7TDMI V4T                       | Base updated    | Address of Inst + 12                           |

| ARM9TDMI v4T                       | Base restored   | Address of Inst + 12                           |

# Table 2-4. ARM9TDMI Implementation Option

The ARM9TDMI is code-compatible with the ARM7TDMI, with two exceptions:

- The ARM9TDMI implements the base restored data abort model, which significantly simplifies the software data abort handler.

- The ARM9TDMI fully implements the instruction set extension spaces added to the ARM (32-bit) instruction set in architecture v4 and v4T.

These differences are explained in more detail below.

#### DATA ABORT MODEL

The base restored data abort model differs from the base updated data abort model implemented by ARM7TDMI. The difference in the data abort model affects only a very small section of operating system code, the data abort handler. It does not affect user code. With the base restored data abort model, when a data abort exception occurs during the execution of a memory access instruction, the base register is always restored by the processor hardware to the value the register contained before the instruction was executed. This removes the need for the data abort handler to unwind any base register update which may have been specified by the aborted instruction. The base restored data abort model significantly simplifies the software data abort handler.

#### Instruction set extension spaces

All ARM processors implement the undefined instruction space as one of the entry mechanisms for the undefined instruction exception. That is, ARM instructions with opcode[27:25] = 0b011 and opcode[4] = 1 are undefined on all ARM processors including the ARM9TDMI and ARM7TDMI.

ARM Architecture v4 and v4T also introduced a number of instruction set extension spaces to the ARM instruction set. These are:

- Arithmetic instruction extension space

- Control instruction extension space

- Coprocessor instruction extension space

AMSUNGC

Load/store instruction extension space.

Instructions in these spaces are undefined (they cause an undefined instruction exception). The ARM9TDMI fully implements all the instruction set extension spaces defined in ARM Architecture v4T as undefined instructions, allowing emulation of future instruction set additions.

# **ARM940T CP15 REGISTERS**

#### **CP15 Register Map Summary**

The ARM940T incorporates CP15 for system control. The register map for C15 is shown in Table 2-5.

| Register | Function                             | Access                            |

|----------|--------------------------------------|-----------------------------------|

| 0        | ID code/Cache type                   | See note below                    |

| 1        | Control                              | Read/write                        |

| 2        | Cacheable                            | See note below                    |

| 3        | Write buffer control                 | Read/write                        |

| 4        | Reserved                             | Undefined                         |

| 5        | Protection region access permissions | See note below                    |

| 6        | Protection region base/size control  | See note below                    |

| 7        | Cache operations                     | Write only. Reads unpredictable   |

| 8        | Reserved                             | Undefined                         |

| 9        | Cache lockdown                       | Read/write                        |

| 10-14    | Reserved                             | Undefined                         |

| 15       | Test                                 | Not accessed in normal operations |

#### Table 2-5. CP15 Register Map

NOTE: Register locations 0, 2, 5, and 6 each provide access to more than one register. The register accessed depends upon the value of the opcode\_2 field. See the register descriptions that follow for further information.

# **Register 0: ID code**

This is a read-only register which returns a 32-bit device ID code. The ID code register is accessed by reading CP15 register 0 with the opcode\_2 field set to any value other than 1. For example: MRC cp15, 0, rd, c0, c0,{0,2-7}, returns ID register

The contents of the ID code are shown in Table 2-6.

#### Table 2-6. ID Code Register

| Register Bits | Function             | Value                 |

|---------------|----------------------|-----------------------|

| 31:12         | Implementor          | 0x41 (identifies ARM) |

| 23:16         | Architecture version | 0x2                   |

| 15:4          | Part number          | 0x940                 |

| 3:0           | Version              | 0x1                   |

## **Register 0: Cache type**

This is a read-only register which allows operating systems to establish how to perform operations such as cache cleaning and lockdown. Future ARM cached processors will contain this register, allowing RTOS vendors to produce future-proof versions of their operating systems.

The cache type register is accessed by reading CP15 register 0 with the opcode\_2 field set to 1. For example: MRC cp15, 0, rd, c0, c0, 1; returns Cache type register